Performance Analysis of Fault Tolerant Irregular MINs

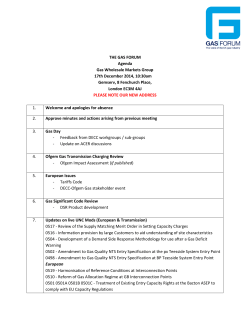

Performance Analysis of Fault Tolerant Irregular MINs Deepti Malhotra Department of Computer Science &Engineering Thapar Institute of Engineering and Technology Patiala, 147004, INDIA E-mail [email protected] Abstract: The effectiveness of parallel or distributed systems is often determined by its communication network. Multistage Interconnection Network plays a vital role on the performance of the multiprocessor system. This paper introduces a class of fault tolerant Multistage Interconnection Network (MINs) named as Modified Double Tree Network (MDOT), Four Tree Network (FT), Modified Four Tree Network (MFT), Fault Tolerant Double Tree Network (FDOT) and an attempt has been made to analyze these different irregular Multistage Interconnection Networks in terms of no of stages, no of switches, fault-tolerance, cost-effectiveness, path length, reliability and performance. A MFT and FDOT network can provide a “full access” capacity in presence of multiple faults. FDOT network supports on-line repairability and is cost-effective than other fault-tolerant Multistage Interconnection Networks with a similar fault-tolerant capability. FT network is a single switch fault-tolerant.If both switches in a loop are simultaneously faulty then clearly some sources are disconnected from some destinations. Keywords: Multistage Interconnection Network, Double Tree Network, Four Tree Network, Modified Four Tree Network, Modified FT, Fault Tolerant Double Tree Network. I. INTRODUCTION With the present state of technology, building multiprocessor systems with hundreds of multistage processors is feasible. The Multistage Interconnection Networks (MINs) are an important part of these systems that enable the processors to communicate with themselves and with the memory modules. In MINs, the fixed interstage connections exist between the adjacent stages with a number of switches at each stage that are dynamically set to establish desired connections to route the requests from the source to the destination. Multistage interconnection networks (MINs) achieve the full access property with far fewer connections and hence have become very popular. Rinkle Aggarwal Department of Computer Science &Engineering Thapar Institute of Engineering and Technology Patiala, 147004, INDIA E-mail [email protected] Many ways of providing fault-tolerance to the multistage interconnection networks (MINs) have been proposed in the literature. The basic idea for fault-tolerance is to provide multiple paths for a source-destination pair, so that alternate paths can be used in case of faults in a path. Fault-tolerance is the ability of the network to operate even in the presence of faults. A network may be provided with fault-tolerance by providing rnultiple paths between an input and output pair. This can be done by increasing the number of stages, by providing multiple links between stages, increasing the size of the switch, portioning a unique path network into several subnetworks and incorporating multiple copies of a basic network. The organization of the paper is as follows: Section II comprises of DOT network. Section III provides details of MDOT network. Section IV provides description of FT network. Section V comprises of MFT network. Details and design of FDOT network are proposed in Section VI. Comparison of these networks on the basis of different parameters is proposed in Section VII. Section VIII comprises of some important terms used in the paper. Finally conclusions are given in Section IX. II. DOT NETWORK As the name indicates, the DOT network consists of two full binary trees with a common root. Though the DOT network is irregular and has fewer switching elements than a conventional Multistage Network, it maintains the full access property. Unlike regular MINs, the DOT network has paths of varying lengths between pairs of input and output terminals. Certain pairs of input and output terminals, called the favourite pairs, have a shorter path length between them than others. Hence, the DOT network is expected to perform better than a conventional MIN. The DOT network of size 8X8 is shown in figure1. The DOT network is a 2(log N) - 1 stage interconnection network having 2n+1 - 3 switching elements. It is an irregular interconnection network in the sense that the number of switching elements (SE) differs from stage to stage. The SEs in stage j are numbered from 0 to N/2j+1 – 1 starting from the topmost SE. The upper and lower input (output) terminals of an SE i are numbered as, 2i and 2i+1, respectively. As shown in Fig. l, the SEs of the DOT network have an interconnection pattern which is a combination of two trees (in opposite directions) having a common root node in the centre. The interconnection between the SEs is described below. in each stage j, 0 <= j < n - 1 for each SE i, 0 <= i < 2n-j-1 , with i0 = 0 output 2i Æ input 2i of stage 2n - 2 - j output 2i+1 Æ1 input [2i + 1)/2] of stage j+1 for each SE i, 0 <= i < 2n-j-1 , with i0 = 1 output 2i Æ input 2i/2 = I of stage j + 1 output 2i +1Æinput 2i +1 of stage 2n - 2 - j in each stage j, n - 1 <= j < 2n - 2 for each SE i, 0 < i < 2j-n+1 output 2i Æ input 4i + 1 of stage j + 1 output 2i Æ1 + input 4i + 2 of stage j + 1 It can be seen that, when the central switch (CS) of an N x N DOT network is in the through or straight state, the network is split into two disjoint N/2 x N/2 networks of 2n - 2 stages. Each of the two N/2 x N/2 subnetworks will have two central switching elements, namely the left central switch (LCS) and the right central switch (RCS).The central switches of the jth N/2 x N/2 subnetwork are labelled LCSi, j and RCSi, j, respectively. In general, the central switches of the N/2i x N/2i, (0 <= i <= n - 1) subnetwork will have the labels, LCSi, j and RCSi, j respectively, where j, (0 <= j <=2i - 1) represents the subnetwork number (with the numbering starting from the top most subnetwork and proceeding downwards). LCS0,0 is the same as RCS0,0 and is referred to as the CS of the network. Because of the central switches, the DOT network is blocking with limited permutation capability. The structure of the DOT network allows multiple paths of varying lengths (in terms of the number of SEs passed through) between a pair of source and destination terminals. III. MDOT NETWORK MDOT network is an Irregular Multistage Interconnection Network .It consists of a right and a left half. Each half of the network resembles a binary tree. The left and right trees are mirror images of each other. MDOT network of size 2n X 2n has 2n source and 2n destination and 2n-1 stages. Further, it has (2n+1 -3) switches. Each of the stage i and 2n-i have exactly 2n-1 switches of size 2X2 for i= 1, 2…n. The MDOT network of size 8X8 is shown in figure2. IV. FT NETWORK The FT network of size 2n X2n contains two identical groups G0 and G1 each consisting of a MDOT network of size 2n-1 X 2n -1 ,which are organized one above the other. The two groups are formed based on the most significant bit (MSB) of the source-destination terminals. Thus, half of the source destination terminals with MSB 0 fall into group G0 and others having MSB 1 fall into the group G1 . The FT network of size 2n X 2n has (2m-1) stages and total of (2m+2 -6) switches with 2n-1. of size 2X2 and rest of size 3X3. There are 2n multiplexers and an equal no of demultiplexers of 2X1 and 1X2 sizes respectively. Both the stages i and 2m-i in the group have 2n-i-1 switches and are numbered as 1,2…..2n-i-1 (where i = 1,2…,m , m = log2 N/2 and N = 2n ). Every 3X3 SE in a stage forms a loop with the corresponding numbered 3X3 SE of other sub –network in the same stage. Every source and destination is connected to both the subgroups by means of multiplexers and demultiplexers. In case the primary path is busy or faulty, requests will be routed through secondary path in the sub-network. FT network is single switch fault-tolerant. If both switches in a loop are simultaneously faulty then clearly some sources are disconnected from some destinations.FT network of size 16X16 is shown in figure3. V. MFT NETWORK Modified FT network of size 16X16 has one stage and two switch less compared to the FT network. It contains total of (2m+2-8) switches and (2m-2) stages .It contains the multiplexers and demultiplexers equal to FT network. The 2X1 multiplexers are connected in such a manner that each multiplexers between pair of sources have all the bits (sn-2…..s2s0) equal except the bit s1 . The 2X1 demultiplexers are so connected that each multiplexer is connected to destinations having all bits (dn-1…d1) the same. MFT network of size 16X16 is shown in figure4. VI. FDOT NETWORK An FDOT-k network of size NXN is designed by dividing N inputs and N outputs into k disjoint partition of N/k sources and N/k destinations where k (>=2) and N (>k) are the powers of 2.There are k independent subnetworks, and an extra one, such that a connection path between each source-destination pair can be established via any one of the subnetwork. All the (k+1) subnetworks are of identical type. The extra subnetwork helps to enhance fault-tolerant capability and to keep a desired level of performance even in the presence of faults. Each source and destination are linked to all the (k+1) subnetworks via kX1 multiplexers and 1Xk demultiplexers.An FDOT-k consists of (2n-1) number of stages and (k+1) (2n+1-3) number of switching elements, where n = log2 N/k. FDOT network of size 8X8 is shown in figure 5. Figure1: DOT Network of size 8X8 Figure2: MODIFIED DOT NETWORK Figure3: FOUR TREE NETWORK OF SIZE 16X16 Figure4: MODIFIED FOUR TREE NETWORK OF SIZE 16X16 Figure5: FDOT NETWORK OF SIZE 8X8 VII. COMPARISON OF IRREGULAR MINS In this paper MINs are compared as: A. On the basis of the Hardware Structure: such as no of stages, no of switches, no of switches per stage and no of multiplexers/demultiplexers. Comparisons are shown in table I. B. On the basis of Performance Parameters. Comparisons are shown in table II. TABLE I: COMPARISON ON THE BASIS OF HARDWARE Sr No. Characteristics 1 Full Form 2 MDOT FT MFT FDOT modified double tree Four tree modified four tree Fault-tolerant double tree Number of stages For 2nX2n network no. of stages are (2n-1) where N= 2n For 2nX2n network no. of stages are (2m-1) where m=log2N/2 & N= 2n For 2nX2n network no. of stages are (2m-2) where m=log2N/2 & N=2n For 2nX2n network no. of stages are (2n-1) where n= log2N/k ,k(>=2) are independent subnetworks and N(>k) 3 Number of switches (2n+1-3) switches (2m+2-6) switches (2m+2-8) switches (k+1)(2n+1-3) switches 4 Number of switch per stage Stage i &(2n-i) have exactly 2n-1 switches where i=1,2,…..,n Stage i &(2m-i) in the group have 2n-i-1 switches where i=1,2,…..,m Stage i &(2m-i-1) in the group have 2n-i switches where i=1,2,..,n+1 Stage i & 2(n1)-i have exactly (k+1). 2n-i-1 switching element for i=0,1…,(n-1) 5 Number of multiplexers & demultiplexers multiplexers & demultiplexers are not used 2n multiplexers & 2n demultiplexers are used 2n multiplexers & 2n demultiplexers are used number of multiplexers & demultiplexers are (N+2n) TABLE II: COMPARISON ON THE BASIS OF PERFORMANCE PARAMETERS Sr No. Characteristics MDOT FT MFT FDOT 1 Fault –Tolerant Not faulttolerant, the central switch is critical and presence of a single fault breaks down the system completely. It is single switch fault-tolerant. If both switches in a loop are simultaneously faulty then clearly some sources are disconnected form some destinations. If both switches in a loop are simultaneously faulty then even some sources are connected to the destinations. K switch fault – tolerant means it can provide a connection for any source-destination pair in the presence of any instance of upto k faults in the network. 2 Cost-Effectiveness It is also costeffective FT is more costeffective than MFT.Proposed cost is (9.75 2n+1-54) Proposed cost of MFT is (9.75 2n+1-72) More cost-effective than other faulttolerant MINs. Its cost is (k+1)(2n+3+2N-12) 3 Path Length It is a unique path network where only a single path exists between any input-output pair. The network has multiple path of different lengths between an inputoutput terminal pair Multiple paths of varying lengths are available between each sourcedestination pair. If [(sn-1 d n-1) + (sn-2 d n-2) d2)] +…+ (s2 is zero. Then Minimum path is available along with the other possible pathlength Multiple paths of varying lengths are available between each sourcedestination pair. If [(sn-1 d n-1) +(sn-2 d n-2) +…+(sj dj)] is zero (where 1<=j<=(n1)) then all paths of length equal to or greater than 2j are possible else paths of length 2n1(i.e. longest path is possible only. 4 Reliability & Performance It is less reliable because single switching element is present and breakdown of switching element leads to the breakdown of the network that has derogatory effect on the performance of the system. The network has improved reliability. The improved reliability obtained from the multiple paths depends upon how effectively the alternate paths are used by the routing algorithm. MFT has improved reliability & performance than FT. FDOT-k is k faulttolerant, so it is quite reliable as compared to the other networks containing nearly same amount of hardware. It possesses the property of on-line repairability. VIII. IMPORTANT TERMS USED IN THE PAPER Fault–Tolerant: A fault tolerance multistage interconnection network provides service routing even under the faults. Fault-tolerance is the ability of the network to operate even in the presence of faults. The basic idea for fault-tolerance is to provide multiple paths for a source-destination pair, so that alternate paths can be used in case of faults in a path. Path-Length: The path length p, of a path between an input terminal and an output terminal in a MIN is the number of SEs encountered by a message sent along that path. It gives the information about the different pathlengths possible between the source-destination pair. On-line Repairable: A network is said to be On-line repairable that if some faults develop in any component in the network, then the faulty component can be simply replaced by the new one without causing a break-down in the system. Cost-Effectiveness: To estimate the cost of a network the assumption is that the cost of a switch used in a network is proportional to the number of cross-points within a switch. [3] [4] [5] [6] [7] [8] [9] Reliability: It is defined to be the probability of existence of at least one fault-free path between a given pair of input and output. [10] IX. CONCLUSION [11] In this paper irregular fault-tolerant Multi-Stage Interconnection Networks named Modified double tree network, four tree network, Modified four tree network, and Fault-tolerant double tree network have been proposed and analyzed. Further, these different irregular multistage interconnection networks are compared in terms of different parameters like no of stages, no of switches, fault-tolerance, cost-effectiveness, path length, reliability. In MDOT single switching element is present and breakdown of switching element leads to the breakdown of the network as a result the performance of the network. MFT and FDOT can achieve significant tolerance to faults and good performance with relatively low costs and simple control schemes. REFERENCES [1] [2] G.B. Adams III, D.P. Agrawal, H.J. Siegel, “A survey and comparison of Fault- Tolerant Multistage Interconnection Network”, Computer, Vol.20, No.6, June 1987, pp.14-27. G.B. Adams III, D.P. Agrawal, H.J. Siegel, “The extra –stage cube: a fault-tolerant interconnection network for supersystems, I.E.E.E Transactions on Computers, 31, 1982, pp.443-454. [12] P.K Bansal, K Singh, and R.C. Joshi, “Routing and path length algorithm for a cost-effective fourtree multi-stage interconnection network”, International J.Electronics, 1992,(1), pp.107-115. P.K Bansal, K Singh, and R.C. Joshi, G.P. Siroha, “Fault-tolerant double tree network”, Proceedings of International conference 1.E.E.E. INFOCOM, 1991, pp.462-468. CP. kruskal. And M Snir., “Performance of multistage interconnection networks for multiprocessors”, I.E.E.E. Transactions on Computers, 1987, (20), pp. 30-40. J.P. Shen ,”Fault Tolerance Analysis of several interconnection networks”, Proc. of International Conference on Parallel Processing, August 1982, pp. 102-112. Laxmi N.Bhuyan, Qing Yang and Dharma P. Aggrawal, “Performance of multiprocessor Interconnection Networks”, I.E.E.E Computer, Vol. 22, Feb. 1989, 25-37. J.H.Patel,”Performance of Processor-Memory Interconnections for Multiprocessors”, IEEE Trans. Comp., Vol.30, Oct. 1981, pp.771-780. N.Tzeng, P.Yew, C.Zhu, “A Fault- Tolerant scheme for Multistage Interconnection Networks”, Proc. of 12th International Symposium on Computer Architecture, June 1985, pp.368-375. V.P. Kumar, S.M Reddy, “Design and Analysis of Fault Tolerant Multistage Interconnection Networks with low-link Complexity”, Proc. 12th International R.Potapalli Yashovardhan, P. Aggarwal Dharma, “On the design of efficient Multistage Interconnection Network”, IEEE Trans. Computers, 1996. Laxmi N. Bhuyan , Qing Yang and Dharma P. Aggarwal, “Performance of multiprocessor Interconnection Networks” IEEE Computer, Vol. 22, Feb. 1989, 25-37 .

© Copyright 2026