General Outline

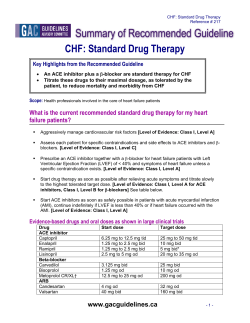

General Outline 9 ULSI technologies: manufacturing 9 Radiation effects in devices and technologies 9 Radiation Hardness-By-Design (HBD) techniques for ASICs 9 130nm technology node for High Energy Physics: vendor, properties, radiation effects IN2P3 school, May 2005 Federico Faccio - CERN 1 Hardness-By-Design (HBD) techniques Outline 9 Foreword 9 TID: Total Ionizing Dose z z TID and scaling Solutions 9 SEEs: Single Event Effects z z SEEs and scaling Solutions 9 Summary & Conclusion IN2P3 school, May 2005 Federico Faccio - CERN 2 Foreword 9 What we will be talking about: z z z z ASICs (application-specific ICs) CMOS technologies only Effects: TID, SEU, SEL How to conceive ASICs able of surviving to and functioning in a radiation environment IN2P3 school, May 2005 Federico Faccio - CERN 3 Is it a problem for me? Which TID can be considered as “safe”? Is there a dependence on design (logic vs analog, …)? Is there variability with time (different results for different production lots)? 9 Is there a technological dependence on the TID tolerance? 9 9 9 0.5μm 0.35μm 0.5μm 0.25μm 1.E -03 1.E -04 Leakage current [A] 1.E -05 1.E -06 1.E -07 1.E -08 1.E -09 1.E -10 1.E -11 1.E -12 0 50 100 150 200 250 T o ta l D o s e [k ra d (s iO 2 )] IN2P3 school, May 2005 Federico Faccio - CERN 4 Risk management 9 9 9 9 As seen before, there are many variables influencing the final radiation hardness of an IC The “safer” the circuit is designed, the more “expensive” it is (area, performance, complexity, …) Risk reduction comes at some cost In the following, a procedure to RELIABLY designing radiation tolerant ASICs is presented. It reposes on physics, not on specific process recipes, hence it gives very predictable results. IN2P3 school, May 2005 Federico Faccio - CERN 5 Hardness-By-Design (HBD) techniques Outline 9 Foreword 9 TID: Total Ionizing Dose z z TID and scaling Solutions 9 SEEs: Single Event Effects z z SEEs and scaling Solutions 9 Summary & Conclusion IN2P3 school, May 2005 Federico Faccio - CERN 6 Radiation effects and tox scaling Damage decreases with gate oxide thickness Oxide trapped charge Interface states N.S. Saks et al., IEEE TNS, Dec. 1984 and Dec. 1986 IN2P3 school, May 2005 Federico Faccio - CERN 7 Tendency confirmed 9 Gate oxides in commercial CMOS technologies did follow the curve drawn by Saks and co-workers! Technology node (μm) DVth/Mrad(SiO2) [V/rad(SiO2)] 1.E+02 1.6 1.2 0.8 0.5 0.5 - A 0.5 - B 0.35 0.25 - A 0.25 - B tox^2 1.E+01 1.E+00 1.E-01 1.E-02 1.E-03 1 10 100 tox (nm) IN2P3 school, May 2005 Federico Faccio - CERN 8 Hardness-By-Design (HBD) techniques Outline 9 Foreword 9 TID: Total Ionizing Dose z z TID and scaling Solutions 9 SEEs: Single Event Effects z z SEEs and scaling Solutions 9 Summary & Conclusion IN2P3 school, May 2005 Federico Faccio - CERN 9 Radiation hard CMOS processes “Usual solution”: technology hardening TID hardness is guaranteed but 9 Low volume in fabs => yield can be low, and unreliable radiation performance for large quantities 9 Cost is very high 9 Very limited number of processes still available today, and risk of unavailability in the long run 9 Analog performance often not very good 9 9 IN2P3 school, May 2005 Federico Faccio - CERN 10 Radiation-tolerant layout (ELT) Leakage path G S IN2P3 school, May 2005 G D D Federico Faccio - CERN S 11 Function of the guardring + N+ WELL CONTACT VSS VSS VDD OXIDE+ + + + + + + P+ GUARD + + + + + + N+ SOURCE N WELL SUBSTRATE IN2P3 school, May 2005 The heavily doped p+ guardring “interrupts” possible conductive paths (inverted p substrate), hence preventing inter-device leakage currents Federico Faccio - CERN 12 Radiation tolerant approach ΔVth ∝ toxn + ELT’s and guard rings = TID Radiation Tolerance IN OUT Example layout for an inverter p+ guard ring VSS IN2P3 school, May 2005 metal polysilicon n+ diffusion p+ diffusion Federico Faccio - CERN VDD 13 Effectiveness of ELTs 0.7 μm technology - W/L = 2000/1.5 1.E-02 1.E-03 1.E-04 1.E-05 ID [A] 1.E-06 1.E-07 1.E-08 1.E-09 1.E-10 Prerad 1.E-11 After 1 Mrad 1.E-12 After 1 Mrad (ELT) 1.E-13 -1 -0.5 0 0.5 1 1.5 2 2.5 3 3.5 VG [V] IN2P3 school, May 2005 Federico Faccio - CERN 14 Effectiveness of ELTs 0.25 μm technology - W/L = 30/0.4 - ELT 1.E-01 1.E-03 ID [A] 1.E-05 1.E-07 1.E-09 Prerad and after 13 Mrad 1.E-11 1.E-13 -0.60 -0.22 0.16 0.54 0.92 1.30 1.68 2.06 2.44 2.82 V G [V] IN2P3 school, May 2005 Federico Faccio - CERN 15 Field oxide leakage FOXFET 14.4/2.6 without gate, with guardring 0.5 μm technology ID [A] 1.E-10 1.9 Mrad 1.E-11 anneal 420 Krad Prerad 1.E-12 0.0 0.5 1.0 1.5 2.0 2.5 3.0 VD [V] IN2P3 school, May 2005 Federico Faccio - CERN 16 Advantages of this approach 9 Relies on physics (thickness of gate oxide): not process-dependent 9 Allows for using state-of-the-art technologies: z z z z Low power High performance High throughput, high yield, short turnaround times Low cost IN2P3 school, May 2005 Federico Faccio - CERN 17 Difficulties for this approach 9 Peculiar ELT behaviour z z z Modeling of ELT (size W/L?) Limitation in aspect ratio Asymmetry 9 Lack of commercial library for digital design 9 Loss of density 9 Yield and reliability??? IN2P3 school, May 2005 Federico Faccio - CERN 18 Modeling of ELTs (1) Source c d' d Drain IN2P3 school, May 2005 L 2 Federico Faccio - CERN +2 + 19 Modeling of ELTs (2) d – d’ 2 W 2α 1– α = 4 + 2K +3 d’ L eff Leff ln 1.13•ln 1 α d’ – 2αLeff ( ) Ldrawn 0.28 0.36 0.5 1 3 5 IN2P3 school, May 2005 Estimated (W/L)eff 14.8 11.3 8.3 5.1 3 2.6 Extracted (W/L)eff 15 11.2 8.3 5.2 3.2 2.6 1 shape only supported (size of “c” fixed) 9 Custom routines and layers integrated in design kit for extraction/design checking/computation 9 Federico Faccio - CERN 20 Limitation in the aspect ratio Aspect ratio = W/L 15 14 Effective aspect ratio 13 12 11 10 9 8 7 6 5 4 3 2 0 1 2 3 4 5 6 7 8 9 10 Gate Length [[μm] m] IN2P3 school, May 2005 Federico Faccio - CERN 21 Asymmetry (1) L = 0.28 μm GDI = 11.9 μS GDO = 9.6 μS 1.4E-04 1.2E-04 I drain [A ] 1.0E-04 Drain Inside Drain Outside 8.0E-05 6.0E-05 4.0E-05 2.0E-05 0.0E+00 0.0 0.5 1.0 1.5 2.0 2.5 Vds [ V ] IN2P3 school, May 2005 Federico Faccio - CERN 22 Asymmetry (2) O u tp u t C o n d . [u S ] 100.0 ELT Drain Inside ELT Drain Outside Normal Transistor 10.0 L (μm) ΔG/GDI 0.28 0.36 0.5 1 3 5 1.0 0.1 19 % 23 % 33 % 53 % 70 % 75 % 0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5 Gate Length [um ] IN2P3 school, May 2005 Federico Faccio - CERN 23 Lack of commercial library (1) Radiation tolerant design : z Use of enclosed NMOS transistors z Use of guard rings to isolate all n+ diffusions at different potentials (including n-wells) NAND3 IN2P3 school, May 2005 Federico Faccio - CERN 24 Lack of commercial library (2) 9 Example of core cells IN2P3 school, May 2005 Federico Faccio - CERN 25 Lack of commercial library (3) 9 IN2P3 school, May 2005 Federico Faccio - CERN List of Library Standard Cells 26 Existing libraries 9 List is not exclusive: z CERN in 0.25μm • “Daughter” libraries in PSI, LBL, Fermilab z z IMEC (for ESA) in 0.18μm Mission Research Corporation (for Aerospace Corporation) in 0.18μm IN2P3 school, May 2005 Federico Faccio - CERN 27 Loss of density 9 Radiation Tolerant techniques introduce a ~70% layout area overhead Inverter 2-in NAND 2-in NOR Static D-F/F Static D-F/F SR Standard 33.6 μm2 46.0 μm2 47.8 μm2 153.0 μm2 188.1 μm2 Rad-Tol 50.9 μm2 119.0 μm2 80.0 μm2 533.1 μm2 572.0 μm2 Penalty 34 % 61 % 41 % 71 % 75 % 0.8 μm 9 0.24 μm Gate density is 8 times larger when compared to a 0.8μm technology z Example: ring oscillator with 1280 inverters in 0.8 and 0.25mm technologies (0.25 uses the CERN radtol library) a) b) Area: IN2P3 school, May 2005 Federico Faccio - CERN 650,400 μm 82,350 μm 28 Yield and reliability? 9 9 9 Construction analysis performed on several chips Circuits produced, qualified and tested in thousands (100 different designs!) No concern on yield or reliability found yet… IN2P3 school, May 2005 Federico Faccio - CERN 29 “Large” scale production 9 Relatively large number of project in production, for quantities up to almost 600 wafers (200mm size). Total production in excess of 3000 wafers. Volume per project 700 500 400 300 Production summary 200 900 100 800 0 18 16 N of wafers produced N of wafers produced A PV 25 A tla s pix C MS Pix H PT DC T ra c k e rS e rv i c e Me d A li ce ip ix Pix e ls H AL 25 MG P A A DC 4 1 24 0 F e n ix D iC a Sy L HC B Pix GO L A NN D tmr o c -s B e et le A li c e TO F P asc Am P re s h o we MP W r 11 C RT A ll MP W 15 MP W 14 700 14 N of projects in production 600 12 500 10 400 8 300 6 200 4 100 2 0 0 Y 1999 Y 2000 Y 2001 Y 2002 Y 2003 Y 2004 Y 2005 Y 2006 IN2P3 school, May 2005 Federico Faccio - CERN 30 N of projects in production Volume (wafers) 600 ASICs examples 9 9 9 9 APV25: readout of Silicon tracker detector of the CMS experiment 128 channels, analog output Alice Pixel1, readout of silicon pixel detector of the ALICE experiment 2.1cm2, 8000 analog channels, 13M transistors IN2P3 school, May 2005 Federico Faccio - CERN 9 GOL, optical link driver (serializer (serializer + laser driver) @ 1.6 Gbit/s 9 CCU, control chip for the CMS tracker detector (fully digital chip, 120kgates) 31 Other edgeless designs 9 Other “edgeless” transistor designs are possible ! G G from D.Mavis, MRC S D Ringed Source S D S Ringed Interdigitated G S D Butterfly IN2P3 school, May 2005 Federico Faccio - CERN 32 Hardness-By-Design (HBD) techniques Outline 9 Foreword 9 TID: Total Ionizing Dose z z TID and scaling Solutions 9 SEEs: Single Event Effects z z SEEs and scaling Solutions 9 Summary & Conclusion IN2P3 school, May 2005 Federico Faccio - CERN 33 SEU and scaling: forecast • VDD reduced • Node C reduced • New mechanisms for SEU P.E. Dodd et al., IEEE TNS, Dec. 1996 From the above, it looks like the SEU problem worsens with scaling IN2P3 school, May 2005 Federico Faccio - CERN 34 SEU and scaling: reality All sources agree: DRAM sensitivity has been scaling down (cell area scaling has outpaced the decrease in stored charge). 9 Picture somewhat less clear for SRAMs 9 P.Hazuka et al (work funded by Intel) developed a model to predict SER scaling with Lg. The results suggest that the per-bit sensitivity decreases –at least- linearly with Lg 9 Overall: FIT/MB decreases, but FIT/chip increases 9 9 Not only Vdd and node capacitance have to be taken into account: sensitive area and charge collection efficiency are also important and change with technology generation! IN2P3 school, May 2005 Federico Faccio - CERN 35 SEL and scaling 9 9 9 Retrograde wells Trench isolation VDD reduced VDD contact All these issues help in preventing SEL, but they might not be always effective VDD source n + VSS source VSS contact n + p + p + R2 n well decrease R1 p substrate IN2P3 school, May 2005 R5 R6 R4 R3 decrease Federico Faccio - CERN 36 Hardness-By-Design (HBD) techniques Outline 9 Foreword 9 TID: Total Ionizing Dose z z TID and scaling Solutions 9 SEEs: Single Event Effects z z SEEs and scaling Solutions 9 Summary & Conclusion IN2P3 school, May 2005 Federico Faccio - CERN 37 Solutions: SEU 9 9 9 Technology level: epitaxial substrates, SOI,… Cell design: SEU-tolerant FFs or memories Redundancy z z 9 Triple Modular Redundancy (TMR): triplication and voting Encoding (EDAC) Always to be considered at system level IN2P3 school, May 2005 Federico Faccio - CERN 38 Cell design (1) 9 Increase the critical charge by increasing the node capacitance: z Design larger transistors – also more driving strength IN2P3 school, May 2005 Federico Faccio - CERN 39 Cell design (2) 9 Increase the critical charge by increasing the node capacitance: Add “extra” capacitors z • Metal/metal to avoid loosing space 2 σ [cm /bit] 1.E-06 1.E-07 "standard" SR "oversized" SR "overloaded" SR 1.E-08 0 10 20 30 40 50 60 70 80 2 LET [MeVcm /mg] IN2P3 school, May 2005 Federico Faccio - CERN Upset rates in proton environment: - twofold decrease for the “oversized” - tenfold decrease for the “overloaded” 40 Cell design (3) DICE (Dual Interlock Cell) 9 Dual Interlock ensures SEU protection against hit on one node 9 Writing in the cell requires access to 2 nodes 9 0 IN2P3 school, May 2005 1 Federico Faccio - CERN 0 1 0 41 Cell design (4) 9 DICE cell weakness: z Recovery time needed after SEU • Output glitch • A rising edge of the clock during recovery time can store wrong data in the following pipeline stage z z Local clock buffers Charge collection by multiple nodes is not negligible! (in 90nm technology, just 10x SEU rate improvement) IN2P3 school, May 2005 Federico Faccio - CERN 42 Cell design (5) 9 Use special cell architectures z Temporal sampling with internal clock delays (after Mavis) effective against digital SET • Transient can only be captured by 1 latch • Sensitive to transients on clock line • Many variations to this concept exist (one can delay data instead of clock, for instance) IN D Q DFF CLOCK OUT ΔT 2ΔT D Q DFF D Q DFF Temporal Sampling IN2P3 school, May 2005 Federico Faccio - CERN MAJ Asynchronous Voting 43 Solutions: SEU 9 9 9 Technology level: epitaxial substrates, SOI,… Cell design: SEU-tolerant FFs or memories Redundancy z z 9 Triple Modular Redundancy (TMR): triplication and voting Encoding (EDAC) Always to be considered at system level IN2P3 school, May 2005 Federico Faccio - CERN 44 Redundancy: TMR (1) 9 9 9 9 Triplication with 1 voter The state machine is instantiated 3 times, with 1 voter An SEU can corrupt the output of one of the blocks, but majority voting restores the correct state An error in the voter instead corrupts the state! IN2P3 school, May 2005 Federico Faccio - CERN Combinatorial Logic Register Combinatorial Logic Register Combinatorial Logic Register Majority Voter 45 Redundancy: TMR (2) 9 Triplication with 3 voters 9 The state machine is instantiated 3 times, with 3 voters An SEU can corrupt the output of one of the blocks, but majority voting restores the correct state An error in one of the voters is also restored 9 9 9 Combinatorial Logic Register Majority Voter Combinatorial Logic Register Majority Voter Combinatorial Logic Register Majority Voter This seems a lot of additional transistors, but sometimes the designer can find more “compact solutions”. This is shown in the following example. IN2P3 school, May 2005 Federico Faccio - CERN 46 Example of TMR in registers (1) A majority voter can necessitate a large number of transistors. Since 3 voters are required to protect the data from errors in the voter, the overall area penalty can be very large! 9 One compact solution for the voter is in the schematic below: 9 9 9 9 9 IN2P3 school, May 2005 Federico Faccio - CERN Combinatorial Logic Register Majority Voter Combinatorial Logic Register Majority Voter Combinatorial Logic Register Majority Voter Very compact layout 14 transistors (better than XOR+MUX style) Fast z 2 logic levels only z Possible to save the inverter (2 transistors less) Still 3 voters are needed, for a minimum of 36 transistors 47 Example of TMR in registers (2) 9 9 To save some transistors, it is possible to merge the voter in the register, and make a single cell Each “super cell” will then have 3 inputs and 1 output with merged connections between them Register Register Register in1 Majority Voter Majority Voter B C in2 D0 Q D1 D2 A out1 A A C B D0 Q D1 D2 out2 B Majority Voter in3 D0 Q D1 D2 A B D0 Q D1 D2 C out3 C ck IN2P3 school, May 2005 Federico Faccio - CERN 48 Example of TMR in registers (3) Merging of the voter can be done at different levels The example below, for a dynamic FF, illustrates it. The first part of the FF cell is shown in the left picture, with its timing diagram. A first level of merging is achieved by integrating the voter in the input inverter, as shown in the right picture. This does not really save transistors with respect to a separate voter 9 9 9 Clock = in1 D0 Q D1 D2 B C in1 a C B B out1 A b in A in1 C b Clock a a in b precharge IN2P3 school, May 2005 a a in Federico Faccio - CERN 49 Example of TMR in registers (4) 9 A “deeper” merging, where the voter is moved inside the FF, leads to considerable area saving in1 D0 Q A aB D1 a aC D2 out1 aA A b aB aA aC aA aC aB in aA IN2P3 school, May 2005 Federico Faccio - CERN This integration of the voter in the cell “only” costs 5 additional transistors! For 3 “super cells”, the penalty for the voter decreases from 36 to 15 transistors! 50 Solutions: SEU 9 9 9 Technology level: epitaxial substrates, SOI,… Cell design: SEU-tolerant FFs or memories Redundancy z z 9 Triple Modular Redundancy (TMR): triplication and voting Encoding (EDAC) Always to be considered at system level IN2P3 school, May 2005 Federico Faccio - CERN 51 Redundancy: encoding (1) 9 Adding redundant information (bits) and encoding-decoding z z z Used for data transmission and for memories Requires complex encoding-decoding logic Several different codes can be used (Hamming, Reed-Solomon, BCH, etc.) Encoder Decoder Memory array (each word with redundant bits) IN2P3 school, May 2005 Federico Faccio - CERN 52 Redundancy: encoding (2) 9 Example: Hamming encoding (1950) k = number of message bits q = number of check (parity) bits n = number of word bits Minimum distance between words = 3 ⇒All valid words in the code differ AT LEAST by 3 bits ⇒It can be used for single error correction, double error detection n = k+q n ≤ 2q-1 30 30 28 26 24 22 20 18 16 k( q) 14 12 10 8 6 4 1 2 0 2 2 IN2P3 school, May 2005 Federico Faccio - CERN 3 4 q 5 30 28 30 26 24 22 20 18 16 n ( q) 14 12 10 8 6 4 2 3 0 5 53 Redundancy: encoding (3) 9 Example: Hamming encoding (1950) Example of encoding for k=8 q=4 n = 12 Encode in a way requiring “as easy as possible” encoding/decoding logic 1. Check bits in powers of 2 positions in the word (position 1,2,4,8) 2. Other word bits are the message bits 3. Each check bit computes the parity for some of the word bits: Position 1: check 1 bit, skip 1 bit, etc. (bits 1,3,5,7,9,11) Position 2: check 2 bits, skip 2 bits, etc. (bits 2,3,6,7,10,11) Position 4: check 4 bits, skip 4 bits, etc. (bits 4,5,6,7,12) Position 8: check 8 bits, skip 8 bits, etc. (bits 8,9,10,11,12) Word to encode: 10101010 word position IN2P3 school, May 2005 . 1 1 . 1 1 . 0 1 0 0 . 1 0 1 0 1 2 3 4 5 6 7 8 9 10 11 12 Federico Faccio - CERN 54 Redundancy: encoding (4) 9 Example: Hamming encoding (1950) Word to encode: 10101010 Encoded word 1 1 1 1 0 1 0 0 1 0 1 0 position 1 2 3 4 5 6 7 8 9 10 11 12 SEU changes to 1 1 1 1 0 0 0 0 1 0 1 0 Check the parity bits in the received word: Position 1: OK Position 2: wrong Position 4: wrong Position 8: OK The position of wrong bit is the sum of the wrong positions, that is Position 6! IN2P3 school, May 2005 Federico Faccio - CERN 55 Outline 9 9 Foreword: CMOS technologies TID: Total Ionizing Dose z z z 9 Effects (reminder) Solutions Trends in state-of-the-art technologies SEEs: Single Event Effects z z z Effects (reminder) SEEs and scaling Solutions • SEU • SEL 9 Conclusion IN2P3 school, May 2005 Federico Faccio - CERN 56 Reducing SEL sensitivity The best solution is to decrease the gain of the parasitic pnpn structure. Technological and layout solution can help in that respect: Technological => use of epitaxial substrates and retrograde wells => use of trench instead of junction isolation Layout => increase the distance between complementary devices => use guardrings => use lots of substrate and well contacts VDD contact VDD source n + VSS guardring VSS source VSS contact p + n + p + p + R2 n well R4 R6 R1 p substrate IN2P3 school, May 2005 R5 R3 Federico Faccio - CERN 57 Hardness-By-Design (HBD) techniques Outline 9 Foreword 9 TID: Total Ionizing Dose z z TID and scaling Solutions 9 SEEs: Single Event Effects z z SEEs and scaling Solutions 9 Summary & Conclusion IN2P3 school, May 2005 Federico Faccio - CERN 58 Summary & Conclusion 9 9 9 9 In state-of-the-art commercial-grade CMOS technologies, reliable radiation tolerance can be achieved with HBD techniques If “natural” TID is insufficient, the use of ELTs and guardrings can “upgrade” it – large effort needed mainly for digital design SEU rates can be decreased with proper engineering (study of environment, introduction of tolerant cells, redundancy, encoding, etc.) and should always be considered at the system level SEL – already unlikely – can be further controlled by careful layout IN2P3 school, May 2005 Federico Faccio - CERN 59 Further reading 9 On Enclosed Transistor Layout: z z z 9 Ph.D. thesis describing results in 0.25μ 0.25μm technology: technology: G.Anelli, G.Anelli, “Conception et caractérisation de circuits intégrés résistants aux radiations pour les détecteurs de particules du LHC en technologies CMOS submicroniques profondes“, Ph.D. Thesis at the Politechnic School of Grenoble (INPG), France, December 2000, availeble on the web at the URL: http://rd49.web.cern.ch/RD49/RD49Docs/anelli/these.html http://rd49.web.cern.ch/RD49/RD49Docs/anelli/these.html Paper containing all references on the work done at CERN on this subject: F.Faccio, F.Faccio, “Radiation Issues in the new generation of high energy physics experiments”, Int. Journal of High Speed Electronics and Systems, Vol.14, No.2 (2004) 379379-399 On SEUSEU-tolerant Cells: z Increased capacitance: • • • z Special SEUSEU-tolerant cells: • • • • • 9 F.Faccio et al., “Single Event Effects in Static and Dynamic Registers in in a 0.25mm CMOS Technology”, IEEE Trans. Nucl. Nucl. Science, Vol.46, No.6, pp.1434pp.1434-1439, December 1999 F.Faccio et al., “SEU effects in registers and in a DualDual-Ported Static RAM designed in a 0.25mm CMOS technology for applications in the LHC”, in the proceedings of the Fifth Workshop Workshop on Electronics for LHC Experiments, Snowmass, September 2020-24, 1999, pp.571pp.571-575 (CERN 9999-09, CERN/LHCC/99CERN/LHCC/99-33, 29 October 1999) P.Roche, F.Jacquet, C.Caillat, J.P.Schoellkopf, "An Alpha Immune and Ultra Low Neutron SER High Density SRAM", proceedings of IRPS 2004, pp671-672, April 2004 R.Velazco et al., “2 CMOS Memory Cells Suitable for the Design of SEUSEU-Tolerant VLSI Circuits”, IEEE Trans. Nucl. Nucl. Science, Vol.41, No.6, p.2229, December 1994 T.Calin et al., “Upset Hardened Memory Design for Submicron CMOS Technology”, Technology”, IEEE Trans. Nucl. Nucl. Science, Vol.43, No.6, p.2874, December 1996 M.N.Liu et al., “Low power SEU immune CMOS memory circuits”, IEEE Trans. Trans. Nucl. Nucl. Science, Vol.39, No.6, p.1679, December 1992 J.Canaris, J.Canaris, S.Whitaker, S.Whitaker, “Circuit techniques for the radiation environment of Space”, IEEE IEEE 1995 Custom Integrated Circuits Conference, p.77 P.Eaton, P.Eaton, D.Mavis et al., “Single Event Transient Pulsewidth Measurements Using a Variable Temporal Latch Technique”, IEEE Trans. Nucl. Nucl. Science, Vol.51, no.6, p.3365, December 2004 On TMR and encoding: z Paper comparing techniques and containing references, to be used as a starting research point: S.Niranjan, S.Niranjan, J.F.Frenzel, J.F.Frenzel, “A comparison of FaultFault-Tolerant State Machine Architectures for SpaceSpace-Borne Electronics”, IEEE Trans. On Reliability, Vol.45, No1, p.109, March 1996 IN2P3 school, May 2005 Federico Faccio - CERN 60 General Outline 9 ULSI technologies: manufacturing 9 Radiation effects in devices and technologies 9 Radiation Hardness-By-Design (HBD) techniques for ASICs 9 130nm technology node for High Energy Physics: vendor, properties, radiation effects IN2P3 school, May 2005 Federico Faccio - CERN 61 130nm technology node for HEP Outline 9 The 130nm technology node 9 Radiation effects in samples from different Foundries 9 CERN Foundry Service in 130nm z z z Specific features Radiation effects Design Kits IN2P3 school, May 2005 Federico Faccio - CERN 62 The 130nm technology node In production since 2000-2001 Still available via “brokers” (Europractice, MOSIS, CMP), but not all versions 9 General common features: 9 9 z z z z z z z z z z “still” available in 200mm wafers (8 inches) 8 levels of copper metallization Logic and analog/RF versions with different devices available 2 oxide thicknesses (core 2-2.2nm and I/O for operation to 2.5V), thin oxides that should be radiation tolerant Wide range of transistors (different dopings) Effective minimum L 0.08-0.09 um Integration achievable of the order of 200kgates/mm2 Very wide range of IP blocks generally available from either the Foundry or third parties Large number of masks, and expensive => NRE between 2.5 and 5 times more expensive than “our” 250nm Projected availability to around 2018 IN2P3 school, May 2005 Federico Faccio - CERN 63 130nm technology node for HEP Outline 9 The 130nm technology node 9 Radiation effects in samples from different Foundries • Core transistors (ELT, linear layout) • I/O transistors (ELT, linear layout) 9 CERN Foundry Service in 130nm z z z Specific features Radiation effects Design Kits IN2P3 school, May 2005 Federico Faccio - CERN 64 Aim and experimental details 9 9 9 9 9 9 AIM: Understanding the natural radiation tolerance of the 130nm node. Testing samples from different Foundries allows to check if observed results are common properties or specific of just “one” particular process Samples from 3 commercial 130nm CMOS processes have been tested Some are Process Monitoring Devices (PMD) from foundry, some custom-designed test ICs NMOS and PMOS transistors, core and I/O devices (different oxide thickness), FOXFETs Testing done at probe station – no bonding required (transistors are extremely fragile and gate oxide can be damaged by bonding) Irradiation with X-rays at CERN up to 100200Mrad, under worst case static bias The CERN X-ray facility Custom-developed test IC IN2P3 school, May 2005 Federico Faccio - CERN 65 Core NMOS transistors, enclosed (ELT) Example: Foundry A 9 1.00E-03 1.00E-04 1.00E-05 1.00E-06 Id (A) The radiation hardness of the gate oxide is such that practically no effect is observed – verified for 2 foundries (A up to 140Mrad, B up to 30Mrad). Id=f(Vgs) curves drop on top of each other after any TID step (see figures) ELT transistors are suitable for SHLC applications: are they really needed? 3Mrad 1.00E-08 136Mrad 2d HT ann 1.00E-10 1.00E-11 1.00E-12 -0.2 0.3 0.8 1.3 Vg (V) PMOS ELT min/012 1.E-03 1.E-04 1.E-05 1.E-06 1.E-07 pre-rad 3 Mrd 40 Mrd 1.E-08 1.E-09 1.E-10 1.E-11 1.E-12 -0.2 IN2P3 school, May 2005 Pre-rad 1.00E-07 1.00E-09 Id (A) 9 NMOS ELT min/0.12 Federico Faccio - CERN 0.3 0.8 Vg (V) 1.3 66 Core NMOS transistors, linear layout (1) Wide transistors (W > 1μm): 9 When the transistor is off or in the weak inversion regime: • Leakage current appears (for all transistor sizes) • Weak inversion curve is distorted z When the transistor is in strong inversion: • No significant change in characteristics IN2P3 school, May 2005 1.E-02 1.E-03 1.E-04 Id (A) z Foundry A, 2/0.12 1.E-05 1.E-06 Pre-rad 3Mrad 136Mrad 2d HT ann 1.E-07 1.E-08 1.E-09 1.E-10 -0.5 Federico Faccio - CERN 0.0 0.5 1.0 1.5 2.0 Vg (V) 67 Core NMOS transistors, linear layout (2) Narrow transistors (W < 0.8μm): 9 When the transistor is off or in the weak inversion regime: • Leakage current appears (for all transistor sizes) • Weak inversion curve is distorted z z Additionally, a Vth shift (decrease) appears for narrow channel transistors The narrower the transistor, the larger the Vth shift. This effect has been called Radiation-Induced Narrow Channel Effect (RINCE) IN2P3 school, May 2005 1.E-03 1.E-04 1.E-05 1.E-06 Id (A) z Foundry A, 0.16/0.12 1.E-07 Pre-rad 3Mrad 136Mrad 2d HT ann 1.E-08 1.E-09 1.E-10 1.E-11 1.E-12 -0.5 Federico Faccio - CERN 0.0 0.5 1.0 1.5 2.0 Vg (V) 68 Core NMOS transistors, linear layout (3) Let’s observe the effect on the leakage current z z z Peak in leakage at a TID of 15Mrad (A and B), similar for all transistor sizes Peaking dependent on dose rate and temperature, difficult to estimate in real environment Different in the 3 technologies 0.16/0.12 0.32/0.12 0.48/0.12 0.8/0.12 2/0.12 10/1 10/10 ELT Foundry A 1.E-06 1.E-07 1.E-08 1.E-09 1.E-10 1.E-11 1.E+05 pre-rad 1.E+06 1.E+07 1.E-06 1.E-07 1.E-07 1.E-08 N_10_013 1.E-09 N_10_10 1.E-08 N_10_012 N_088_012 1.E-09 N_04_013 N_053_012 N_024_013 N_018_013 1.E-10 N_028_012 1.E-10 N_014_013 pre-rad 1.E+09 annealing 1.E-05 Foundry C 1.E-06 1.E-11 1.E+04 1.E+08 TID (rad) Ileak (A) Ileak (A) 1.E-05 Foundry B 1.E-05 Ileak (A) 9 1.E+05 IN2P3 school, May 2005 1.E+06 1.E+07 TID (rd) 1.E+08 N_016_012 1.E+09 1.E-11 1.E+04 pre-rad Federico Faccio - CERN 1.E+05 1.E+06 1.E+07 1.E+08 annealing 1.E+09 TID (rd) 69 Core NMOS transistors, linear layout (4) Let’s observe the effect on the threshold voltage z Peak in Vth shift at a TID of 15Mrad (A and C) z The narrower the transistor, the larger the Vth shift (RINCE) z Peaking dependent on dose rate and temperature, difficult to estimate in real environment z Sample from Foundry B different! Foundry A 0.000 -0.020 -0.040 -0.060 -0.120 -0.140 -0.160 1.E+05 -0.040 -0.060 -0.060 8 Vth (V) -0.040 -0.080 -0.140 1.E+05 1.E+07 annealing 1.E+09 1.E+08 Foundry C 0.000 -0.020 N_10_10 -0.080 N_10_012 N_10_013 N_04_013 N_024_013 N_018_013 N_014_013 -0.120 1.E+06 TID (rad) -0.020 -0.100 016_012 032_012 048_012 08_012 2_012 10_1 10_10 ELT -0.080 -0.100 Foundry B 0.000 ⎝ Vth (V) 0.020 Vth (V) 9 N_088_012 -0.100 N_053_012 N_028_012 -0.120 N_016_012 -0.140 1.E+06 1.E+07 1.E+08 1.E+09 1.E+05 IN2P3 school, May 2005 1.E+06 1.E+07 1.E+08 1.E+09 TID (rd) TID (rd) Federico Faccio - CERN 70 Radiation-induced edge effects - NMOS • The peak at 1-5Mrd in the leakage E field lines and Vth can be explained by the different evolution of charge trapped Polysilicon gate in the bulk of the lateral STI ++ ++ ++ ++ -(positive) and in the interface states STI ++ at the interface between STI oxide - ++ STI and silicon (negative) • At the beginning of irradiation, Oxide trapped charge trapped in the oxide Interface Depletion region charge dominates. With further TID, states interface states eventually dominate. ID The relative contribution will depend Main transistor on T, dose rate, etc. • The narrower the transistor, the Lateral more important the influence of the parasitic charge trapped in the lateral STI and transistor interface on the full depletion region => the more relevant the radiation effects => RINCE 0 VGS IN2P3 school, May 2005 Federico Faccio - CERN 71 Core PMOS transistors, linear layout (1) 9 1.E-05 1.E-06 1.E-07 1.E-08 Pre-rad 3Mrad 30Mrad 136Mrad 1dHT 1.E-09 1.E-10 1.E-11 1.E-12 -0.5 0.0 0.5 1.0 1.5 2.0 Vg (V) 1.E-04 Foundry C, 0.28/0.12 1.E-05 1.E-05 1.E-06 1.E-06 1.E-07 1.E-07 1.E-08 Id (A) Id (A) 1.E-04 Foundry B, 0.14/0.13 1.E-04 Foundry A, 0.16/0.12 Id (A) No change in the weak inversion regime, no leakage An apparent Vth shift (decrease) for narrow channel transistors, more visible in samples from Foundry A z The narrower the transistor, the larger the Vth shift (RINCE) 9 Pre-rad 1.E-08 pre-rad 22.5 Mrd 1.E-09 26 Mrd 1.E-09 89.5 Mrd 100 Mrd 1.E-10 1.E-10 1.E-11 1.E-11 1.E-12 1.E-12 -0.5 0.0 0.5 1.0 1.5 2.0 -0.5 IN2P3 school, May 2005 0.0 0.5 1.0 1.5 2.0 Vg (V) Vg (V) Federico Faccio - CERN 72 Radiation-induced edge effects - PMOS • IN PMOS, the charge trapped in E field lines both oxide traps and interface states Polysilicon gate are positive. Therefore, the threshold voltage of the lateral ++ ++ ++ ++ -+ + - ++ “parasitic” increases steadily and no STI ++ + + leakage or deformation of the STI Id=f(Vgs) curve in weak inversion is observed. Oxide trapped • Nevertheless, in narrow transistors Depletion region Interface charge the charge trapped laterally can states influence the electric field in the ID whole depletion region, inducing and Main transistor apparent Vth shift. •The narrower the transistor, the Lateral more important the influence of the parasitic charge trapped in the lateral STI and transistor interface on the full depletion region => the more relevant the radiation effects => RINCE 0 VGS IN2P3 school, May 2005 Federico Faccio - CERN 73 I/O transistors, ELT 9 Non-negligible effect on the Vth, especially for PFETs Shift larger than what observed in 250nm node in the past… 1.E-02 NMOS min/0.26 1.E-03 Id (A) 9 1.E-04 1.E-05 1.E-06 1.E-07 1.E-08 1.E-09 1.E-10 1.E-11 1.E-12 1.E-13 -0.5 pre-rad 3 Mrd 57 Mrd 190 Mrd 0.0 0.5 1.0 1.5 Vg (V) 2.0 2.5 3.0 1.E-03 Id (A) PMOS min/0.26 1.E-04 1.E-05 1.E-06 1.E-07 1.E-08 1.E-09 1.E-10 1.E-11 1.E-12 -0.5 pre-rad 1 Mrd 3 Mrd 40 Mrd annealing 0.0 0.5 1.0 1.5 2.0 Vg (V) IN2P3 school, May 2005 Federico Faccio - CERN 74 I/O transistors, linear layout z z 9 Peak degradation at 15Mrd observed as well RINCE observed as well Results different for different Foundries, but for all leakage in NMOS starts already at 50-100krad 1.E-03 Foundry A, NMOS 0.36/0.24 1.E-04 1.E-05 1.E-06 1.E-07 1.E-08 1.E-09 1.E-10 1.E-11 1.E-12 1.E-13 pre-rad 300 krd 1 Mrd 27 Mrd 97 Mrd 190 Mrd -0.5 0.0 0.5 1.E-03 1.0 1.5 Vgs (V) 2.0 2.5 3.0 Foundry A, PMOS 2/0.24 1.E-04 1.E-05 1.E-06 Ids (A) Same qualitative effects as for core transistors, but larger impact on transistor parameters Ids (A) 9 1.E-07 1.E-08 1.E-09 pre-rad 1.E-10 1 Mrd 5 Mrd 1.E-11 25 Mrd 1.E-12 65 Mrd 1.E-13 -3.0 -2.5 -2.0 -1.5 -1.0 -0.5 0.0 0.5 Vgs (V) IN2P3 school, May 2005 Federico Faccio - CERN 75 130nm technology node for HEP Outline 9 The 130nm technology node 9 Radiation effects in samples from different Foundries 9 CERN Foundry Service in 130nm z z z Specific features Radiation effects Design Kits IN2P3 school, May 2005 Federico Faccio - CERN 76 Selected Foundry Services supplier 9 9 9 9 Competitive tendering has taken place in 2006 (CERN rules for “frame contracts”) One Foundry has been selected to supply the serviceContract is for 130nm (and beyond) CMOS and BiCMOS CERN will organize MPWs and engineering runs as already provided in the 250nm node In the absence of sufficient demand, MPW service is now accessible via a broker. CERN organizes “grouped” access via the broker, since there is a minimum area to be purchased (10mm2). Grouping allows users to prototype small chips for reasonable charges IN2P3 school, May 2005 Federico Faccio - CERN 77 130nm technology node for HEP Outline 9 The 130nm technology node 9 Radiation effects in samples from different Foundries 9 CERN Foundry Service in 130nm z z z Specific features Radiation effects Design Kits IN2P3 school, May 2005 Federico Faccio - CERN 78 Natural radiation tolerance and its stability 9 9 9 9 The use of ELTs and guardring renders the ASICs tolerant to TID safely and reliably – but the cost is performance (power, area) and effort (custom library) Can we rely on the “natural” tolerance of the technology, such that “standard” layout can satisfy our TID tolerance requirements? The question is complex and answers will be elaborated in the following few slides… NB: Radiation tests have been performed on this technology over time. Available hardware from Q12002 to Q1-2006 (4 samples at different times). In this time frame, the process went through final development and then production phase, possibly with significant changes. Nevertheless, radiation performance is very comparable! IN2P3 school, May 2005 Federico Faccio - CERN 79 Core NMOS transistors REMINDER of main effects: Wide transistor (W>0.8um) Narrow transistor (W>0.8um) 1.E-03 1.E-02 1.E-04 1.E-05 1.E-04 1.E-06 1.E-05 1.E-07 1.E-06 Pre-rad 3Mrad 136Mrad 2d HT ann 1.E-07 1.E-08 1.E-09 1.E-10 -0.5 Id (A) Id (A) 1.E-03 Pre-rad 3Mrad 136Mrad 2d HT ann 1.E-08 1.E-09 1.E-10 1.E-11 1.E-12 0.0 0.5 1.0 1.5 -0.5 2.0 0.0 0.5 1.0 1.5 2.0 Vg (V) Vg (V) Leakage and “distortion” of weak inversion slope => all sizes Influence on “main” transistor also in strong inversion => narrow transistors (RINCE) There is NO sharp frontier between “narrow” and “wide”! RINCEs will be increasingly pronounced for narrower transistors… IN2P3 school, May 2005 Federico Faccio - CERN 80 Core PMOS transistors REMINDER of main effects: NO leakage or distortion of weak inversion curve 1.E-04 1.E-05 1.E-06 Id (A) 1.E-07 1.E-08 Pre-rad 3Mrad 30Mrad 136Mrad 1dHT 1.E-09 1.E-10 1.E-11 1.E-12 -0.5 0.0 0.5 1.0 1.5 2.0 Vg (V) Slight Vth shift for the narrowest transistors only (0.16-0.3um) IN2P3 school, May 2005 Federico Faccio - CERN 81 I/O transistors Results qualitatively similar to Core FETs, but the impact of damage is more important 0.200 1.E-05 0.100 1.E-06 0.000 1.E-07 10/1 -0.100 1.E-08 ELT -0.200 0.36/0.24 0.8/0.24 2/0.24 10/1 10/10 ELT -0.300 -0.400 -0.500 1.E+05 1.E+06 1.E+07 1.E+08 TID (rd) 1.E+09 annealing Ileak (A) NMOS DVth (V) 9 0.36/0.24 0.8/0.24 2/0.24 10/10 1.E-09 1.E-10 1.E-11 1.E-12 1.E+04 1.E+05 1.E+06 1.E+07 1.E+08 annealing 1.E+09 TID (rd) 0 .5 0 0 0 .4 5 0 0 .4 0 0 PMOS DV th (V 0 .3 5 0 0 .3 6 /0 .2 4 0 .8 /0 .2 4 Notice that the radiation effects are important ALSO for ELTs (also for PMOS, not shown here) 2 /0 .2 4 1 0 /1 1 0 /1 0 0 .3 0 0 0 .2 5 0 0 .2 0 0 0 .1 5 0 0 .1 0 0 0 .0 5 0 0 .0 0 0 1 .E + 0 5 1 .E + 0 6 1 .E + 0 7 1 .E + 0 8 a n n1e.E a lin + 0g9 TID (rd ) IN2P3 school, May 2005 Federico Faccio - CERN 82 Radiation-stability of Core NMOS FETs Exactly the same “test structure” was integrated in 2 runs (about 16 months apart). Results are compared here for the leakage current and Vth shift. They are well comparable (charts use the same scales) 1.E-0 6 0.16/0.12 0.32/0.12 0.48/0.12 0.8/0.12 2/0.12 10/1 10/10 E LT 1.E-07 1.E-0 8 1.E-08 Ileak (A) Ileak (A) 1.E-0 7 1.E-06 1.E-0 9 1.E-09 016_012 032_012 1.E-1 0 048_012 1.E-10 064_012 08_012 1.E-1 1 1.E+0 4 pre-rad 2_012 1.E+05 1 .E+0 6 1 .E+0 7 1 .E+0 8 1.E-11 1.E+04 1 .E+0 9 annealing 10_1 1.E+05 1.E+06 TID (rd ) 1.E+07 1.E+08 TID (rad) Run “CuTe2” 10_10 1.E+09 ELT_min_0.12 Run “CuTe3” 0.020 0.020 0.000 0.000 -0.020 -0.020 -0.040 016_012 032_012 048_012 08_012 2_012 10_1 10_10 ELT -0.080 -0.100 -0.120 -0.140 -0.160 1.E+05 1.E+06 1.E+07 1.E+08 annealing 1.E+09 Vth (V) DVth (V) -0.040 -0.060 -0.060 -0.080 -0.100 -0.120 -0.140 -0.160 1.E+05 1.E+06 1.E+07 1.E+08 1.E+09 TID (rad) TID (rd) IN2P3 school, May 2005 016_012 032_012 048_012 064_012 08_012 2_012 10_1 10_10 ELT_min_0.12 Federico Faccio - CERN 83 Radiation-stability of Core PMOS FETs Exactly the same “test structure” was integrated in 2 runs (about 16 months apart). Results are compared here for the Vth shift. They are well comparable (charts use the same scales) 0.100 0.100 016_012 0.080 016_012 08_012 048_012 0.080 2_012 08_012 10_1 2_012 10_10 10_1 0.060 10_10 0.040 ° Vth (V) DVth (V) 0.060 0.020 0.020 0.000 -0.020 1.E+05 0.040 0.000 1.E+06 1.E+07 1.E+08 annealing 1.E+09 -0.020 1.00E+05 TID (rd) 1.00E+06 1.00E+07 1.00E+08 1.00E+09 TID (rd) Run “CuTe2” Run “CuTe3” Results were very comparable for all other devices measured (I/O transistors, resistors, FOXFETs). CONCLUSION: the radiation tolerance does not seem to vary significantly with time, and to be sensitive to small process changes or fluctuations in the processing procedure. IN2P3 school, May 2005 Federico Faccio - CERN 84 Ringed layout Alternative shapes for “hardness by design” based on ringed layout are not very attractive anymore in the 130nm technology node. Influence of charge trapped in the STI can influence the inversion condition of the p- diffusion under the ring, and leakage can still appear (unless the overlap of gate on p- is very large) G D S G S S D D D Butterfly Enclosed Layout Transistor (ELT) 1.E-03 L2 1.E-04 G ++++++++++++ ---------------- 1.E-05 1.E-06 pId (A) S S Ringed Interdigitated G STI ++++++++++++ ---------------p- D S Ringed Source STI G L1 G S D 1.E-07 1.E-08 pre-rad 300 krd 3 Mrd 40 Mrd 1.E-09 1.E-10 1.E-11 1.E-12 -0.5 0.0 0.5 1.0 1.5 2.0 Vg (V) If overlap region L gets small (like L2), L2), inversion in the pp- under the poly can occur under the influence of the electric field induced by the the charge trapped in the STI (indicated with + in the drawings). Therefore Leakage IN2P3 school, May 2005 Federico Faccio - CERN appears 85 Inter-device leakage Measurements based mainly on FOXFETs (only p-doped substrate is relevant). Diffusions/n-wells always at minimum distance compatible with design rules. G S D Metal1 n+ source N+ STI OXIDE STI oxide N+ n+ drain Between n+ diffusions This FOXFET simulates the situation where two neighbor NMOS FETs have terminals at different potential SUBSTRATE G S D n+ source N+ N WELL n+ drain STI OXIDE STI oxide N+ SUBSTRATE S G D n+ source N+ N WELL n+ drain IN2P3 school, May 2005 Between nwell and n+ diff Metal1 Polysilicon STI OXIDE STI oxide N+ N WELL SUBSTRATE Federico Faccio - CERN This FOXFET simulates the situation where an n-well at Vdd is close to an NMOS FET with diffusion at gnd (common case for logic circuits) Between nwells This FOXFET simulates the situation where two n-wells at different potential are close to each other (this happens only in analog, and seldom) 86 Leakage between NFETs 1.E-06 ann 2 weeks 65 Mrd 1.E-07 5 Mrd 3 Mrd pre-rad Ids (A) 1.E-08 1.E-09 FOXFET with W=200um Vgs=2.5V during irradiation 1.E-10 1.E-11 1.E-12 1.E-13 0 5 10 15 20 25 30 35 40 Vgs (V) Leakage increases, but stays in the nA range. This should not impact digital circuits (if their size is not in the 106 NFETs) For analog design, issue only for very low current applications IN2P3 school, May 2005 Federico Faccio - CERN 87 Leakage NFET-Nwell (1) FOXFET with W=200um Vgs=2.5V during irradiation L = twice minimum allowed L = minimum allowed 1.E-03 1.E-03 1.E-04 1.E-04 1.E-05 1.E-05 Ids (A) 1.E-07 1.E-08 1.E-09 1.E-07 1.E-08 1.E-09 1.E-10 1.E-10 1.E-11 1.E-11 1.E-12 1.E-12 0 10 20 30 40 50 60 Vgs (V) 70 80 90 100 pre-rad 100krad 3Mrad 40Mrad annealing 1.E-06 Ids (A) pre-rad 100krad 3Mrad 40Mrad annealing 1.E-06 0 10 20 30 40 50 60 Vgs (V) 70 80 90 100 The leakage level measured should not compromise the functionality of digital circuits (if their size is below a few 100.000 gates) even if space is left at minimum. Leakage peaks at about 3Mrd – as for NMOS leakage! Analog designers should be careful to this possible source of failure. IN2P3 school, May 2005 Federico Faccio - CERN 88 Leakage NFET-Nwell (2) N-well Without guardring Vdd N-well N-well Partial guardring Three layout approaches have been tested in small logic blocks: -Standard (no separation) -Full p+ guardring -Guardring only where possible (without cutting poly connections between N and PFETs) Irradiation results show that partial guardring is good enough to improve tolerance considerably IN2P3 school, May 2005 Vdd Full guardring 1.0E-04 1.0E-05 NoGuard FullGuard PartialGuard I (A) Vdd 1.0E-06 1.0E-07 Federico Faccio - CERN 1.E+04 1.E+05 1.E+06 1.E+07 1.E+08 TID (rad) 89 Leakage Nwell-Nwell 1.E-03 1.E-04 1.E-05 Ids (A) 1.E-06 1.E-07 1.E-08 prerad 100krad 3Mrad 65Mrad ann 2 weeks 1.E-09 1.E-10 1.E-11 FOXFET with W=200um Vgs=2.5V during irradiation 1.E-12 0 5 10 15 Vgs (V) 20 25 30 The leakage increase is maximum at about 3Mrd (as for NFET leakage!). This leakage has to be considered when designing analog circuits – especially when using N-well resistors or triple-well transistors. IN2P3 school, May 2005 Federico Faccio - CERN 90 Forward-biased diodes Devices typically used in bandgap reference voltage circuits. Two different layout used for the same area of diffusion (STI-bound): -Small perimeter (one large diffusion) -Large perimeter (parallel of large number of narrow fingers). Irradiation performed under direct bias = 0.7V Large perimeter 1.E-02 1.E-03 1.E-02 1.E-04 1.E-04 1.E-05 1.E-05 1.E-06 65 Mrd 1.E-07 25 Mrd 1.E-06 3 Mrd 1 Mrd 500 krd 1.E-09 500 krd 1.E-10 5 Mrd 1.E-08 1 Mrd 1.E-09 25 Mrd 1.E-07 5 Mrd 1.E-08 65 Mrd I (A) I (A) Small perimeter 1.E-03 pre-rad pre-rad 1.E-10 1.E-11 1.E-11 1.E-12 0.3 0.4 0.5 0.6 Vforward (V) 0.7 0.8 0.3 0.4 0.5 0.6 Vforward (V) 0.7 0.8 Use the smallest perimeter possible in all cases, and at largest injection level! IN2P3 school, May 2005 Federico Faccio - CERN 91 Diffusion resistors 9 Two n+ diffusion resistors designed and measured: z z Minimum width, nominal R=15.03 KΩ W=1.5um, nominal R = 2.52 KΩ 9 Measured values 17.12 and 2.52 KΩ (tolerance on minimum width is larger!) 9 Irradiated up to 65Mrd, with changes of the order of 1% IN2P3 school, May 2005 Federico Faccio - CERN 92 Why all previous results are worst case (1) 1. Relevance of dose rate All results shown refer to high “laboratory” dose rates typically above 20krd/min. In real applications, the dose rates will be 2-3 orders of magnitude below. Since the radiation response is governed by the combination of oxide trapped charge and interface states, the overall damage depends on temperature and dose rate. 1.E-03 1.E-06 1.E-04 1.E-05 1.E-06 Ids (A) Leakage (A) 1.E-07 1.E-08 1.E-07 1.E-08 1.E-09 1.E-09 1.19krd/min 1.E-11 27.5krd/min 1.E-10 0.E+00 prerad HDR LDR 1.E-10 1.E-12 0 2.E+06 4.E+06 6.E+06 8.E+06 1.E+07 5 10 15 Vgs (V) 20 25 30 TID (rad) 0.48/0.12 NFET leakage at different dose rates: the increase is considerably smaller, and reaches the peak value at lower TIDs, for the smaller dose rate IN2P3 school, May 2005 Current of FOXFETs with n-wells (size=200/min) at two very different dose rates: 24.4krd/min (HDR) and 65rd/min (LDR). Again, current is much smaller at low dose rate. Federico Faccio - CERN 93 Why all previous results are worst case (2) 1. Relevance of dose rate All results shown refer to high “laboratory” dose rates typically above 20krd/min. In real applications, the dose rates will be 2-3 orders of magnitude below. Since the radiation response is governed by the combination of oxide trapped charge and interface states, the overall damage depends on temperature and dose rate. TEST circuit: 16kbit SRAM designed with a memory generator (commercial design, no ELT or guardring, and dense layout). 1.4 1.2 VDDmin [V] 1 0.8 0.6 LDR 0.4 HDR HDR+annealing 0.2 0 0 2 4 6 Total Ionising Dose [Mrad] IN2P3 school, May 2005 8 10 VDDmin is the minimum supply voltage for errorfree functionality at 10MHz. Before irradiation, VDDmin is about 875mV. With irradiation at 24.4krd/min (HDR), VDDmin increases and peaks at 1-6Mrd, to decrease when the TID reaches 10Mrd. With irradiation at 65rd/min (LDR), the increase in VDDmin is very marginal. Federico Faccio - CERN 94 Why all previous results are worst case (3) 1. Relevance of applied bias All results shown on NFETs and FOXFETs have been obtained with DC “worst case” bias: -NFETs: all terminals grounded except gate at Vdd (1.5V) -FOXFETs: all terminal grounded except gate at 2.5V Bias has an important influence on the degradation, as shown in the results below from M.Silvestri (Dept. of Information Engineering, University of Padova, Italy): the radiation-induced increase in leakage depends strongly on applied bias. I/O NFETs Core NFETs 1.E-05 1.E-06 0.48/0.12 Vgs=1.5V 1.E-08 0.36/0.24, Vgs=0V 0.36/0.24, Vgs Pulsed 1.E-07 I leak (A) I leak (A) 1.E-06 0.48/0.12 Vgs=0.75V 0.48/0.12 Vgs=0V 1.E-07 0.36/0.24, Vgs=Vdd 0.36/0.24, Vgs=Vdd/2 1.E-08 1.E-09 1.E-10 1.E-11 1.E-09 1.E-12 pre-rad 1.E+05 1.E-10 1.E+05 pre-rad IN2P3 school, May 2005 1.E+06 1.E+07 1.E+08 1.E+09 TID (rad) 1.E+06 1.E+07 TID (rad) 1.E+08 1.E+09 Pulsed=digital-like (1MHz, 50% duty cycle) Federico Faccio - CERN 95 Single Event Upset /bit) Sensitivity has been tested twice: -With protons on a sample provided by the foundry (16k x 16 SRAM) in 2001 -With heavy ions on a 16kbit SRAM designed using the commercial memory generator 1.E-07 -No SEL ever observed Cross-section (cm 2 8.E-14 s [cm2/bit] 6.E-14 4.E-14 1.E-08 0.13um SRAM @ 1.5V 1.E-09 Weibull 0.13SRAM 0.25um SRAM Weibull 0.25SRAM All bits 0 2.E-14 1.E-10 0 All bits 1 5 10 15 20 25 30 35 40 45 50 2 LET (MeV/cm mg) 0.E+00 0 10 20 30 40 Proton Energy [MeV] 50 60 70 Custom SRAM irradiated with Heavy Ions, and compared to the cross-section measured Foundry sample irradiated with monofor the SRAM in the “CERN Radiationenergetic protons. The cross-section curve Tolerant” library in 0.25um. The 130nm has been obtained with Vdd=1.5V, and SRAM has a much lower LET threshold. In shows no significant difference for “all 1” or an LHC-like environment, this translates in “all 0” patterns, and large sensitivity at low increased sensitivity (15-30 times larger!). energy 96 IN2P3 school, May 2005 Federico Faccio - CERN Summary for designers (1) 9 Analog design z Core FETs ok, however • Avoid narrow transistors (RINCE) • Use ELTs for devices in weak/moderate inversion z Isolation • Neighbor NFETs: ok unless very small current • Nwells surrounded by guardring if the Nwell is sensitive to leakage (small current) and if neighbor NFETs are sensitive to small leakage • Generally enclose with guardrings nodes sensitive to small leakage currents z Diodes • Use forward-biased diodes with max perimeter/area ratio and at max injection z I/O FETs are quite sensitive to TID, expect large leakage and Vth shifts IN2P3 school, May 2005 Federico Faccio - CERN 97 Summary for designers (2) 9 Digital design z Core gates • Use of the commercial library cells should be OK unless the circuit requires the ultimate performance from the technology. This still needs to be confirmed by a real demonstrator. • If custom cells needed, same recommendation as for analog design z I/O cells • The suitability of using the commercial library cells still has to be assessed – only 1 test on few cells has been made so far (result good, but not very representative) IN2P3 school, May 2005 Federico Faccio - CERN 98 Summary for designers (3) 9 Single Event Effects z SEU • The sensitivity is larger than for the 0.25um technology, and mitigation techniques are required for SLHC applications z SEL • No evidence in any test, and very unlikely due to technology (dopings, STI) and voltage supply. Nevertheless, limit resistance to Vdd and Gnd by placing always lots of contacts across the circuit. z SEGR • Although this should not be an issue, sensitivity will be tested later in 2007 (with an heavy ion irradiation on dedicated test structures). IN2P3 school, May 2005 Federico Faccio - CERN 99 130nm technology node for HEP Outline 9 The 130nm technology node 9 Radiation effects in samples from different Foundries 9 CERN Foundry Service in 130nm z z z Specific features Radiation effects Design Kits IN2P3 school, May 2005 Federico Faccio - CERN 100 Well proximity effect 9 High energy well implants result in significant scattering of dopants at the well edge, increasing the net doping level and hence threshold voltage for FETs near a well edge z z The effect is modeled by 1 parameter (which is extracted for post-layout simulations), for estimation – simulation will not be very precise, and it will not depend on the specific layout The use of good design practices for sensitive devices is necessary – place the sensitive devices far from the wells Well FET1 FET2 Vth1 different than Vth2! IN2P3 school, May 2005 Federico Faccio - CERN 101 Isolation-induced stress 9 STI induces compressive strain in silicon, which alters mobility of FETs z z z Ids increases for NFETs, decreases for PFETs This effect is modeled for simulation purposes with two parameters, which can be hand calculated (geometric size to measure in the layout) Extraction from layout is fully supported for post-layout simulation IN2P3 school, May 2005 Federico Faccio - CERN Effect depends on distance of channel from STI STI STI Compressive strain 102 Gate damage due to plasma charging (1) 9 9 9 Many processes step for wafer manufacturing take place in a plasma Isolated metal stripes in a non-uniform plasma get charged at different potentials. The wafers substrate is at one only potential (typically grounded), and an electric field builds up in the oxide isolating the metal from the substrate In the absence of any current from substrate to metal, large voltage differences can be reached – exceeding breakdown of the isolation oxide if this is thin (such as the gate oxide) Non-uniform plasma NonSi wafer IN2P3 school, May 2005 Federico Faccio - CERN Metal stripes Isolation oxide 103 Gate damage due to plasma charging (2) 9 9 9 9 Before the voltage differences reaches breakdown, a current starts flowing across the thin oxide (Fowler-Nordheim tunneling). Current is from electrons injected from substrate to metal This current roughly needs to compensate for flux of positive ions on metal from the plasma. The larger the flux, the larger the current required If large area of metal is exposed to ions, the flux on the metal is large. If the metal is connected to a small area of thin oxide, the FN tunneling current per unit area needs to be large => large voltage across the gate oxide THIS IS CALLED AN ANTENNA! This condition leads to damage to the gate oxide, with consequences on the transistor performance => Vth shift, gate dielectric leakage and increased oxide reliability failure Large ion flux from the plasma Thin oxide area where FN tunneling current flows Large metal area Pre-Metal Dielectric Poly STI STI Si wafer IN2P3 school, May 2005 Federico Faccio - CERN 104 Gate damage due to plasma charging (3) 9 9 To avoid damage, Design Rules limit the allowable ratio of PC/Metal to thin oxide area. This applies individually to all metal layers (it is not cumulative across layers) Solutions to avoid damage: z z Add “tie-down” diodes, connected via M1 to the PC (in this case, the limit ratio from the design rules still applies but the tie-down diode area sums – with multiplication coefficient – to the thin oxide area). At wafer processing temperatures, diodes are very conductive and allow current to flow from metal to substrate Introduce “hops” to next metal level. Before the “hop”, only the area of the metal already connected to the thin oxide counts for the antenna. When processing the next metal level, only the (small) area of the “hop” counts for antenna. TieTie-down diode Long metal1 line IN2P3 school, May 2005 Metal 1 connection Metal 2 “hop” Long metal1 line Federico Faccio - CERN Metal 1 connection 105 Copper dendride formation 9 This is a complex effect that can take place during processing of copper metal layers z z 9 Potential differences built across wells (n and p- wells) can generate currents in the solutions where processing related to a copper metal layer is taking place The induced currents will form “dendrides” around the copper metal line connected to the well, which can lead to shorts to neighbor lines in the same metal level To prevent this to happen, Design Rules have been introduced z Large well Small metal connected to the well Dendrides Ratio of metal to well area has to be large IN2P3 school, May 2005 Federico Faccio - CERN 106 Pattern Density 9 STRICT requirements exist for density of each of the following layers: RX (active area), PC (poly), all metals Requirements are both for the full chip (global rules) and for any small area of it (local rules) z z 9 9 Global rules set the limit – upper and lower density – for the full chip Local rules set the limit – upper and lower density – for areas about 100um wide stepped by about 50um across the full design After tape-out, automatic routine at the Foundry will fill in all layers (“filling”), and produce holes in copper layers (“cheesing”). This is unavoidable Some consequences: z z Example: It is not possible to place “exclude” shapes over area where filling is not wanted. To prevent random metal shapes to be placed over sensitive portion of the design (for instance, where matching is important), cover the sensitive area with uniform metal Some designs that produce excessive local density CAN NOT be manufactured. Example: regions with too large usage of RX. This error is spotted by running a check that predictively estimates the final densities after filling. IN2P3 school, May 2005 Federico Faccio - CERN Large array of large transistors (for instance, a large current mirror) 100um 9 150um Local RX density migh be eccessive here! The design HAS to be modified or it will be rejected from fabrication! 107 Check procedure before tape-out 9 Due to antenna, dendride formation, filling and other complex rules, the checking procedure before tape-out requires several steps just for Design Rule Check (DRC) z z z z Check “ground rules” (GR), or rules mainly related to geometrical requirements Check floating gates and antennas to ensure rules related to plasma damage and dendride formation are satisfied Check global density Check (predictively) local density – the design can be filled at the Foundry to meet all local density requirements All these checks can be performed with Assura (Diva has very limited use for checking). Calibre should also be able to do the job, but we have no experience with it 9 NB: procedure to get “waivers” as we were used with the quarter micron is now much heavier and given the complexity of the technology the risk is also higher 9 IN2P3 school, May 2005 Federico Faccio - CERN 108 Digital design flow The complexity of the technology, its high performance, and the need for minimizing expensive prototyping cycles drives the need for sophisticated tools for digital design 9 A full library is available from a commercial supplier, but how to merge it with the foundry design kit in an optimized and standard design flow? 9 The task of rationalizing the digital design flow and to providing a common platform for design tools has been outsourced to Manhattan Routing Inc. (MRE) 9 Chip design (Verilog) Physical implementation Physical verification Manhattan Routing Digital Design Kit IN2P3 school, May 2005 Federico Faccio - CERN 109 The MRE Digital Design Flow in detail Synthesis dc_shell Placement psyn_shell Post Route Opt pks_shell ECO First Encounter Floorplanning First Encounter Placement Opt pks_shell Hold Fx pks_shell IPO Route nanoroute Clock Tree Gen fects IPO Route nanoroute Extraction Fire & Ice (qx) Post CTS Opt pks_shell Extraction Fire & Ice (qx) SI Analysis celtic_ndc Route nanoroute SI Analysis celtic_ndc Timing Analysis pt_shell Extraction Fire & Ice (qx) Timing Analysis pt_shell SI Analysis celtic_ndc Timing Analysis pt_shell Manhattan Routing Inc. IN2P3 school, May 2005 Federico Faccio - CERN GDS Editor dfII Physical Verification calibre 110 User point of view The design flow uses specific tools 9 Users shall use the same tools, and the appropriate versions of those, to be able to run the flow correctly 9 z 9 Tools and versions used in the latest release of the Design Kit (V1.3): 1-week courses with limited attendance (10 people) are organized periodically at CERN. 3 such courses have already been given by MRE personnel, and another one is planned IN2P3 school, May 2005 Federico Faccio - CERN 111 130nm technology node for HEP Summary 9 9 9 CERN will offer a Foundry Service, as already done in the 250nm node, for the 130nm both CMOS (mixed-signal) and BiCMOS (with SiGe HBTs) can be offered Radiation tolerance of the CMOS technology: z z z 9 9 9 9 It has been tested extensively, and a dedicated HBD digital library does not seem needed A set of recommendation to the use of the technology for designs that have to operate in a radiation environment is available The stability of the natural radiation tolerance will be monitored frequently Cadence-based PDK is available Digital library is available Both PDK and library are distributed within a “Design Kit” from Manhattan Routing Inc., together with a Design Flow for complex digital design CERN-organized MPW runs will start as soon as demand for silicon is sufficient to bring price to competitive level. In the meanwhile, frequent runs are accessible via a broker (CERN can act as contact for such runs) IN2P3 school, May 2005 Federico Faccio - CERN 112

© Copyright 2026