How To Prepare Designs for 65 nm MirrorBit GL and Eclipse

How To Prepare Designs for 65 nm MirrorBit® GL and

65 nm MirrorBit® EclipseTM GL Product Families

Application Note

By: Doug Kearns

1. Introduction

Spansion continues to extend the MirrorBit® GL family of 3V NOR Flash with two additional GL families based

on 65 nm MirrorBit technology. The S29GL-R family is a close copy of the existing 90 nm S29GL-P family and

the S29GL-S family will incorporate the MirrorBit® EclipseTM architecture to the GL Flash portfolio. Spansion

has developed these families with migration in mind and customers can prepare current projects in

development to allow use of these additional families. This document will outline the product differences that

will require attention to facilitate migration to these additional GL family products.

2. GL Family Feature Comparison

Table 2.1 provides an overview of the differences between the various high density MirrorBit GL families. The

65 nm MirrorBit Eclipse GL family will bring improved program and erase performance to high density

MirrorBit NOR applications while maintaining basic hardware and software compatibility to allow use on

existing designs. The feature differences will be discussed individually in Section 3.

One underlying difference between the current MirrorBit GL and future 65 nm products is the use of an

internal micro controller to manage flash activities instead of a hard-wired state machine. The benefit of this

approach is improved performance and feature additions. The trade off with this approach is an increase in

the time required for the device to self-configure when power is applied. The differences in Power On Reset

timing will be discussed in detail in Section 4. The differences in AC & DC specifications are detailed in

Section 5.

Table 2.1 GL Family Feature Comparison (Sheet 1 of 2)

Family

S29GL-N

S29GL-P

S29GL-R

S29GL-S

Process Node

110 nm

90 nm

65 nm

65 nm

Introduction

2005

2007

2009

2010

Density

128 Mbit

√

√

√

256 Mbit

√

√

√

512 Mbit

√

√

√

1024 Mbit

√

√

2048 Mbit

√ (multi-die)

√

√

√ (multi-die)

Sector Size

128KB

√

√

√

√

Data Size

Bus Width

x8/x16

x8/x16

x8/x16

x16

Read Page

16 Byte

16 Byte

16 Byte

32 Byte

Write Buffer

32 Byte

64 Byte

64 Byte

512 Byte

Packaging

56-TSOP

√

√

√

√

64-BGA

√

√

√

√

Asynchronous

√

√

√

√

OTP Area

256 Byte

256 Byte

512 Byte

1024 Byte

Other

Publication Number Designs_for_GL_Products_AN

Revision 04

Issue Date April 14, 2010

A pplication

Note

Table 2.1 GL Family Feature Comparison (Sheet 2 of 2)

Family

S29GL-N

S29GL-P

S29GL-R

S29GL-S

Write Protect

√

√

√

√

√

√

√

√

√

√

√ (1)

√

Read Protect

Unlock Bypass

√

√

Multi-Sector Erase

√

√

Data Polling

√

√

Status Register

Accelerated Programming

√

√

Multi-pass Programming

√

√

Note:

1. S29GL-N, S29GL-P and S29GL-S families support unlimited multi-pass programming utilizing either write buffer or single word write

commands. S29GL-R does not support multi-pass programming (see Single Word and Multi-pass Write Buffer Programming

on page 13).

3. Feature Difference Discussion

3.1

Density

The S29GL-R family is available in monolithic 512 and 1024 Mbit densities only.

The S29GL-S family is available in monolithic 128, 256, 512 and 1024 Mbit densities. The 2048 Mbit density

is a same-die-stack package consisting of two 1024 Mbit die whose access is controlled by address input

A27.

Customers currently using the S29GL128P and S29GL256P should prepare for migration to the S29GL-S

equivalent density device.

3.2

Sector Size

The S29GL-R and S29GL-S families have 128 KB uniform sectors, consistent with the S29GL-N and

S29GL-P.

3.3

Data Size

The S29GL-R has x8/x16 selectable data bus width, consistent with the S29GL-N and S29GL-P. When the

BYTE# input is pulled high, the device will operate with a 16-bit wide data bus. When BYTE# is pulled low, the

device will operate with an 8-bit data bus. If the device is always used in Byte mode, it is recommended to pull

the unused data bus I/O (DQ[15:8]) to high or low via a resistor on the PCB, to minimize noise injection and

power consumption on the unused inputs.

The S29GL-S only supports x16 data bus width. The BYTE# input on previous generations of MirrorBit GL

devices (pin 53 on 56-TSOP and pad F7 on 64-BGA) will be reserved for future use on the S29GL-S. The

BYTE# input on existing designs should be pulled high to force operation in x16 data mode to enable

migration to the S29GL-S.

3.4

Read Page Size

The S29GL-R has a 16-byte (8 word) read page buffer, consistent with the S29GL-N and S29GL-P.

The S29GL-S has a 32-byte (16 word) read page buffer, which is double the depth of the S29GL-N and

S29GL-P to facilitate larger processor cache line fill operations. No software modifications are required to

operate with 16-byte maximum page transfers supported by the S29GL-N and S29GL-P.

Software can be modified to take advantage of the deeper read page buffer on the S29GL-S by querying the

CFI programming buffer depth register at address 4Ch (x16 address bus reference) and configuring software

to perform additional page read cycles.

2

Designs_for_GL_Products

April 14, 2010

Ap pl ic atio n

3.5

No t e

Write Buffer Size

The S29GL-R has a 64-byte (32 word) write buffer, the same depth as the S29GL-P and double the depth of

the S29GL-N. No software modifications are required to operate with up to a 32-byte maximum write buffer fill

supported by the S29GL-N family.

The S29GL-S has a 512-byte (256 word) write buffer, eight times the depth of the existing S29GL-P and

sixteen times the depth of the existing S29GL-N. No software modifications are required to continue use of a

64-byte or 32-byte write buffer fill supported by the S29GL-N and S29GL-P.

Software can be modified to take advantage of the deeper write buffers by querying the CFI programming

buffer depth register at address 2Ah (x16 address bus reference) and configuring software to perform larger

buffer fills.

3.6

Device ID

The 512 Mbit and 1024 Mbit S29GL-R devices will have the same Device ID register values as the monolithic

density versions of the S29GL-N and S29GL-P families. Table 3.1 contains the Device ID values for the GL

families.

The 128 Mbit, 256 Mbit, 512 Mbit and 1024 Mbit S29GL-S devices will have the same Device ID register

values as the monolithic density versions of the S29GL-N and S29GL-P families. Table 3.1 contains the

Device ID values for the GL families.

Existing software that utilizes Device ID to set up software command support does not require modification to

enable basic functionality of the new MirrorBit GL and MirrorBit Eclipse GL families. Use of specific CFI

register reads should be employed to take advantage of new superset features such as wider read page

buffers and write buffers. CFI Process register bits at address 45h (x16 address bus reference) provide insystem determination of the unique GL family (e.g. GL-N: 0010h, GL-P: 0014h, GL-R: 0018h, GL-S: 001Bh).

Table 3.2 provides details of the CFI register values for each GL family. Device ID can only be accessed via

software Autoselect commands on the S29GL-R and S29GL-S not the optional high voltage method

supported on the S29GL-N and S29GL-P.

Table 3.1 Device IDs

Device ID (1)

Density

S29GL-N

S29/GL-P

S29GL-R

S29GL-S

128 Mb

7Eh / 21h / 01h

7Eh / 21h / 01h

7Eh / 21h / 01h

256 Mbit

7Eh / 22h / 01h

7Eh / 22h / 01h

7Eh / 22h / 01h

512 Mbit

7Eh / 23h / 01h

1 Gbit

7Eh / 23h / 01h

7Eh / 23h / 01h

7Eh / 23h / 01h

7Eh / 28h / 01h

7Eh / 28h / 01h

7Eh / 28h / 01h

2 Gbit

7Eh / 48h / 01h

Note:

In x16 mode, DQ[15:8] = 22h for standard S29GL devices.

April 14, 2010

Designs_for_GL_Products

3

A pplication

Note

Table 3.2 CFI Registers (Sheet 1 of 2)

CFI Register

x16 Address

S29GL-N

S29GL-P

S29GL-R

S29GL-S (1)

“QRY” query unique

ASCII string

10h

11h

12h

0051h

0052h

0059h

0051h

0052h

0059h

0051h

0052h

0059h

0051h

0052h

0059h

Primary OEM

Command Set

13h

14h

0002h

0000h

0002h

0000h

0002h

0000h

0002h

0000h

Address for Primary

Extended Table

15h

16h

0040h

0000h

0040h

0000h

0040h

0000h

0040h

0000h

Alternate OEM

Command Set

17h

18h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

Address for Alternate

OEM Extended Table

19h

1Ah

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

VCC Min, Max

1Bh

1Ch

0027h

0036h

0027h

0036h

0027h (2)

0036h

0027h

0036h

VPP Min, Max

1Dh

1Eh

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

Typical timeout per

single write

1Fh

0007h

0006h

0000h

0008h

Typical timeout per

buffer write

20h

0007h

0009h

0009h

0009h

Typical timeout per

block erase

21h

000Ah

0009h

0009h

0008h

0012h (1 Gb),

0011h (512 Mb),

0010h (256 Mb),

000Fh (128 Mb)

Typical timeout for full

chip erase

22h

0000h

0013h

0013h = 1 Gb

0012h = 512 Mb

Max timeout per

single write

23h

0003h

0000h

0003h

0002h

Max timeout per

buffer write

24h

0005h

0005h

0005h

0002h

Max timeout per block

erase

25h

0004h

0003h

0003h

0003h

Max timeout for full

chip erase

26h

0000h

0002h

0002h

0003h

Device size = 2^N

27h

001Ah (512 Mb),

0019h (256 Mb),

0018h (128 Mb)

001Bh (1 Gb),

001Ah (512 Mb),

0019h (256 Mb),

0018h (128 Mb)

001Bh (1 Gb),

001Ah (512 Mb)

001Bh (1 Gb),

001Ah (512 Mb),

0019h (256 Mb),

0018h (128 Mb)

Flash Device

Interface description

28h

29h

0002h

0000h

0002h

0000h

0002h

0000h

0001h

0000h

Max Buffer Write Size

= 2^N

2Ah

2Bh

0005h

0000h

0006h

0000h

0006h

0000h

0009h

0000h

Number of Erase

Block Regions

2Ch

0001h

0001h

0001h

0001h

Erase Block Region 1

Info (1)

2Dh

00FFh (512 Mb),

00FFh (256 Mb),

007Fh (128 Mb)

00FFh (1 Gb),

00FFh (512 Mb),

00FFh (256 Mb),

007Fh (128 Mb)

00FFh (1 Gb),

00FFh (512 Mb)

00FFh (1 Gb),

00FFh (512 Mb),

00FFh (256 Mb),

007Fh (128 Mb)

2Eh

0001h (512 Mb),

0000h (256 Mb),

0000h (128 Mb)

0003h (1 Gb),

0001h (512 Mb),

0000h (256 Mb),

0000h (128 Mb)

0003h (1 Gb),

0001h (512 Mb)

0003h (1 Gb),

0001h (512 Mb),

0000h (256 Mb),

0000h (128 Mb)

Erase Block Region 1

Info (2)

4

Designs_for_GL_Products

April 14, 2010

Ap pl ic atio n

No t e

Table 3.2 CFI Registers (Sheet 2 of 2)

CFI Register

x16 Address

S29GL-N

S29GL-P

S29GL-R

S29GL-S (1)

0000h (1 Gb),

0000h (512 Mb)

0000h (1 Gb),

0000h (512 Mb),

0000h (256 Mb),

0000h (128 Mb)

Erase Block Region 1

Info (3)

2Fh

0000h (512 Mb),

0000h (256 Mb),

0000h (128 Mb)

0000h (1 Gb),

0000h (512 Mb),

0000h (256 Mb),

0000h (128 Mb)

Erase Block Region 1

Info (4)

30h

0002h (512 Mb),

0002h (256 Mb),

0002h (128 Mb)

0002h (1 Gb),

0002h (512 Mb),

0002h (256 Mb),

0002h (128 Mb)

0002h (1 Gb),

0002h (512 Mb)

0002h (1 Gb),

0002h (512 Mb),

0002h (256 Mb),

0002h (128 Mb)

Erase Block Region 2

Info

31h

32h

33h

34h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

Erase Block Region 3

Info

35h

36h

37h

38h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

Erase Block Region 4

Info

39h

3Ah

3Bh

3Ch

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

0000h

“PRI” query unique

ASCII string

40h

41h

42h

0050h

0052h

0049h

0050h

0052h

0049h

0050h

0052h

0049h

0050h

0052h

0049h

Major version number

43h

0031h

0031h

0031h

0031h

Minor version number

44h

0033h

0033h

0033h

0034h

Address Unlock /

Process bits

45h

0010h

0014h

0020h

001Ch

Erase Suspend

46h

0002h

0002h

0002h

0002h

Sector Protect

47h

0001h

0001h

0001h

0001h

Sector Temporary

Unprotect

48h

0000h

0000h

0000h

0000h

Sector Protection

Scheme

49h

0008h

0008h

0008h

0008h

Simul-Op

4Ah

0000h

0000h

0000h

0000h

Burst Mode

4Bh

0000h

0000h

0000h

0000h

Page Mode Type

4Ch

0002h

0002h

0002h

0003h

ACC Supply Min

4Dh

00B5h

00B5h

0000h

0000h

ACC Supply Max

4Eh

00C5h

00C5h

0000h

0000h

WP# Protection

4Fh

0004h (Bottom)

0005h (Top)

0004h (Bottom)

0005h (Top)

0004h (Bottom)

0005h (Top)

0004h (Bottom)

0005h (Top)

Program Suspend

50h

0001h

0001h

0001h

0001h

Unlock Bypass

51h

N/A

N/A

N/A

0000h

Note:

1. For same-die-stacked 2 Gbit GL-S, returned CFI values will be those of the 1 Gbit die in the lower half of the 2 Gbit device address space.

2. For GL-R regulated voltage models, VCC Min CFI register value at offset 1Bh is 0030h.

April 14, 2010

Designs_for_GL_Products

5

A pplication

3.7

Note

Packaging

The S29GL-R is available in 56-TSOP and 64-BGA and has asynchronous operation signal pin out consistent

with the S29GL-N and S29GL-P. The outer dimensions of the 64-ball BGA packaged will be reduced to 9 x 9

mm from 11 x 13 mm which will mandate changes to the surface mount placement program but not to the

printed circuit board layout.

The S29GL-S is available in 56-TSOP and 64-BGA and has asynchronous operation signal pin out consistent

with the S29GL-N and S29GL-P (see Notes attached to Figures 3.1 and 3.2 for specific pin connection

requirements). The 128, 256, 512, and 1024 Mbit density S29GL-S devices use the LAA064 and LAE064

package, which has outer dimensions of 9 x 9 mm, smaller than the 11 x 13 mm outer dimensions of the

LAA064 package used by the S29GL-N and S29GL-P devices. Use of the smaller LAE064 package requires

modification to the surface mount placement program but not to the printed circuit board layout. The samedie-stacked 2 Gbit density uses the 11 x 13 mm LAA064 package, consistent with the S29GL-P and

S70GL02GP.

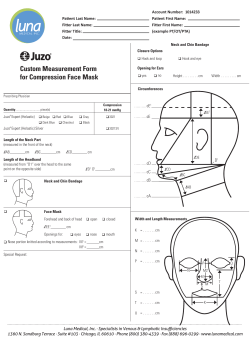

Figure 3.1 GL 64-ball Fortified BGA Signal Land Pattern

Notes:

1. Pads A1, A8, H1 & H8 are Not Connected (internally) and should be left floating.

2. Pads D1, E1 & G1 are Reserved for Future Use and should be left floating.

3. For GL-S, pad F7 is Reserved for Future Use and should be pulled high.

4. For GL-S, pad G7 is DQ15 (only).

5. All active address inputs for a given density device must be controlled, e.g. A[25:0] for x16 S29GL512S. Unused higher order address

inputs can be controlled or left floating. Unused data I/O should be pulled low.

6. For GL-R and GL-S, pad B4 is WP# (only).

6

Designs_for_GL_Products

April 14, 2010

Ap pl ic atio n

No t e

Figure 3.2 GL 56-TSOP Signal Pin Out

Notes:

1. Pins -28 & -30 are Reserved for Future Use and should be left floating.

2. For GL-S, pin -51 is DQ15 (only).

3. For GL-S, pin -53 is Reserved for Future Use and should be pulled high.

4. All active address inputs for a given density device must be controlled, e.g. A[25:0] for x16 S29GL512S. Unused higher order address

inputs can be controlled or left floating. Unused data I/O should be pulled low.

5. For GL-R and GL-S, pin 16 is WP# (only).

3.8

Asynchronous Mode

The S29GL-R supports asynchronous single and page read modes, consistent with the S29GL-N and

S29GL-P.

The S29GL-S supports asynchronous single and page read modes, consistent with the S29GL-N and

S29GL-P. Software can be modified to take advantage of the wider read page buffer on the S29GL-S by

querying the CFI programming buffer depth register at address 98h (x8 address bus reference) or 4Ch (x16

address bus reference) and configuring software to perform additional page read cycles.

3.9

OTP Area

The S29GL-R supports two 256 byte one time programmable Secure Silicon areas, double the available OTP

space on the S29GL-N and S29GL-P.

The S29GL-S supports two 512 byte one time programmable Secure Silicon areas, quadruple the available

OTP space on the S29GL-N and S29GL-P.

3.10

Write Protection

The S29GL-R supports Advanced Sector Protection (ASP) program and erase protection via single voltage,

password, non-volatile and volatile control, consistent with the S29GL-N and S29GL-P.

April 14, 2010

Designs_for_GL_Products

7

A pplication

Note

The S29GL-S supports Advanced Sector Protection (ASP) program and erase protection via single voltage,

password, non-volatile and volatile control, consistent with the S29GL-N and S29GL-P.

Details of ASP program and erase protection implementations can be found in the S29GL-P, S29GL-R and

S29GL-S data sheets.

3.11

Read Protection

The S29GL-R supports Advanced Sector Protection (ASP) read protection via a customer specific ordering

option. The S29GL-N and S29GL-P did not support read protection.

The S29GL-S supports Advanced Sector Protection (ASP) read protection via a customer specific ordering

option. The S29GL-N and S29GL-P did not support read protection.

Details of ASP read protection implementation can be found in the S29GL-R and S29GL-S data sheets.

3.12

Unlock Bypass

The S29GL-R does not support Unlock Bypass mode programming, unlike the S29GL-N and S29GL-P.

The S29GL-S does not support Unlock Bypass mode programming, unlike the S29GL-N and S29GL-P.

Unlock Bypass mode programming is a legacy feature used to decrease the command overhead by 50%

when performing single byte or word programming using the Single byte or word programming command.

Applications using high density GL devices rely on multi-word write buffer programming to maximize

programming throughput. Write buffer programming supports single byte/word programming and has

inherently low effective command overhead. Unlock Bypass mode programming is rarely used in GL Flash

applications. Those applications that do support Unlock Bypass programming will require modification to use

standard single byte/word programming or write buffer programming commands.

3.13

Multi-sector Erase

The S29GL-R does not support multi-sector erase, unlike the S29GL-N and S29GL-P.

The S29GL-S does not support multi-sector erase, unlike the S29GL-N and S29GL-P.

Multi-sector erase is a legacy feature that allowed queueing of multiple sector erase operations within one

command string to minimize command overhead. This is a rarely used function. Those applications that do

support multi-sector erase will require modification to limit sector erase operations to individual sectors only.

3.14

Data Polling

The S29GL-R supports data polling to determine the status of embedded programming and erase operations;

however, unlike the S29GL-N and S29GL-P, it does not support the legacy DQ3 erase time out indicator

function. Applications that utilize DQ3 data polling to validate multi-sector erase command acceptance will

require modification.

The S29GL-S supports data polling to determine the status of embedded programming and erase operations;

however, unlike the S29GL-N and S29GL-P, it does not support the legacy DQ3 erase time out indicator

function. Applications that utilize DQ3 data polling to validate multi-sector erase command acceptance will

require modification. Additionally, DQ0 now provides an indication to system software when a Write-ToBuffer-Abort-Reset command can be issued. This command can only be accepted when DQ0 is high

following an incorrect write buffer load sequence or when status register bit DQ7 is high indicating no

embedded algorithms are active. System software may require modification to accommodate this change.

8

Designs_for_GL_Products

April 14, 2010

Ap pl ic atio n

3.15

No t e

Status Register

The S29GL-R supports Status Register reads to determine embedded program and erase operation status,

in addition to data polling use on the S29GL-N and S29GL-P.

The S29GL-S supports Status Register reads to determine embedded program and erase operation status, in

addition to data polling use on the S29GL-N and S29GL-P.

The status of program and erase operations is provided by a single 16-bit status register. The Status Register

Read command is written followed by one read access of the status register information. The contents of the

status register overlays all addresses in the Flash address space and this overlay is in effect for one read

access only. Subsequent read access to the memory will return array data.

Unlike legacy data polling, use of the status register does not require comparison of sequential polling read

values or to targeted program data to determine embedded algorithm status. The lower byte of the status

register contains bits related to the results - success or failure - of the most recently completed embedded

operation. A Clear Status Register command is provided to reset the last completed embedded operation

portion of the status register. The upper byte of the status register contains bits that indicate dynamic

embedded operation progress relevant during factory troubleshooting. It is recommended that user software

enable capture of the entire status word to enable failure diagnosis. However, the upper bits of status should

be masked or otherwise treated as don't care in terms of evaluating the device status.

Status Register usage is optional and its presence will not inhibit migration to 65 nm MirrorBit GL or MirrorBit

Eclipse GL devices on existing designs. Spansion recommends software modification to take advantage of

this feature by querying the Lower Software Bits at offset xCh in Autoselect mode. If bit 0 is set, Status

Register functionality is supported.

Details of the Status Register implementation can be found in the S29GL-R and S29GL-S data sheets. The

Status Register bit definitions are provided in Table 3.3. Status determination using the Status Register is

illustrated in the flow diagram in Figure 3.3. Provided below is a C source code excerpt from Spansion's Low

Level Driver software (LLD rev 7.2.0) that illustrates how to augment existing drivers to also support Status

Register usage. The Status Register provides a simplified and robust method for status determination and

reduces code required for status determination by ~70%.

Figure 3.3 Status Register Usage Flow Diagram

Write

Status Read

Command

Embedded

Operation

Started

Actively

Programming

or Erasing

Yes

D7 = 0 ?

Read

No

No

Operation =

Erase Suspend?

D6 = 0 ?

Erase in

Suspension

No

Yes

Yes

D5 = 0 ?

No Erase in

Suspension

Operation =

Program Suspend?

Yes

Yes

Yes

Yes

No

Operation =

Program?

Yes

Yes

No

No

Operation =

Erase?

D4 = 0 ?

No

Erase

Successful

Program

Failed

Erase

Failed

D2 = 0 ?

Program

Successful

No

No Program

In Suspension

Program in

Suspension

Yes

DQ2 = 0?

No

Sector Not

Locked

Sector

Locked

Error

April 14, 2010

Designs_for_GL_Products

9

A pplication

Note

Table 3.3 Status Register Definition

3.15.1

SR Bit

Name

Validity

At Reset

“1”

“0”

DQ15:8

Reserved

n/a

n/a

n/a

n/a

Active program or

erase operation

DQ7

Device Ready Bit

Always valid

“1”

No active

embedded

operation

DQ6

Erase Suspend

Status Bit

DQ7 = “1”

“0”

Erase in

suspension

No erase in

suspension

DQ5

Erase Status Bit

DQ7 = “1”

“0”

Erase failed

Erase successful

DQ4

Program Status

Bit

DQ7 = “1”

“0”

Program failed

Program

successful

DQ3

Reserved

n/a

n/a

n/a

n/a

DQ2

Program Suspend

Status Bit

DQ7 = “1”

“0”

Program in

suspension

No program in

suspension

DQ1

Sector Lock

Status Bit

DQ7 = “1”

“0”

Sector locked

error

Sector not locked

DQ0

Reserved

n/a

n/a

n/a

n/a

Status Register Read C Source Example from LLD rev 7.2.0

/****************************************************************

*

* wlld_StatusRegReadCmd - Status register read command

*

* This function sends the status register read command before

* actualy read it.

*

* RETURNS: void

*

* ERRNO:

*/

#ifndef REMOVE_LLD_STATUS_REG_READ_CMD

void wlld_StatusRegReadCmd

(

FLASHDATA * base_addr,

/* device base address in system */

ADDRESS offset

/* address offset from base address */

)

{

FLASH_WR(base_addr, (offset & SA_OFFSET_MASK) + LLD_UNLOCK_ADDR1,

NOR_STATUS_REG_READ_CMD);

}

/****************************************************************

*

* lld_StatusGet - Determines Flash Status for GL-R device

*

* Note: This routine implements both (1) read status and check

* toggles (2) use read status command(GL-R device). The

* enable_status_cmd_g flag switch between these two status get

* methods. When calling this function, the WriteBufferProgramming

* flag needs to be set to 1 if the caller wants to check DQ1 for

* WriteBuffer abort. Then the flag needs to be set back to 0. See

* lld_poll for example of how to use the WriteBufferProgramming

10

Designs_for_GL_Products

April 14, 2010

Ap pl ic atio n

* flag.

*

* RETURNS: DEVSTATUS

*

*/

#define DQ1_MASK

(0x02

#define DQ2_MASK

(0x04

#define DQ5_MASK

(0x20

#define DQ6_MASK

(0x40

*

*

*

*

No t e

LLD_DEV_MULTIPLIER)

LLD_DEV_MULTIPLIER)

LLD_DEV_MULTIPLIER)

LLD_DEV_MULTIPLIER)

/*

/*

/*

/*

DQ1

DQ2

DQ5

DQ6

mask

mask

mask

mask

for

for

for

for

all

all

all

all

interleave

interleave

interleave

interleave

devices

devices

devices

devices

*/

*/

*/

*/

#define DQ6_TGL_DQ1_MASK (dq6_toggles >> 5) /* Mask for DQ1 when device DQ6 toggling */

#define DQ6_TGL_DQ5_MASK (dq6_toggles >> 1) /* Mask for DQ5 when device DQ6 toggling */

DEVSTATUS lld_StatusGet

(

FLASHDATA * base_addr,

ADDRESS

offset

)

{

FLASHDATA

FLASHDATA

FLASHDATA

FLASHDATA

/* device base address in system */

/* address offset from base address */

dq6_toggles;

status_read_1;

status_read_2;

status_read_3;

if( enable_status_cmd_g == 0 )

/* Do not use Read Status */

/* Command */

{

status_read_1 = FLASH_RD(base_addr, offset);

status_read_2 = FLASH_RD(base_addr, offset);

status_read_3 = FLASH_RD(base_addr, offset);

/* Any DQ6 toggles */

dq6_toggles = ((status_read_1 ^ status_read_2) &

Toggles between read1 and read2 */

(status_read_2 ^ status_read_3) &

/* Toggles between read2 and read3 */

DQ6_MASK );

/* Check for DQ6 only */

/*

if (dq6_toggles)

{

/* Checking WriteBuffer Abort condition: Check for all devices */

/* that have DQ6 toggling also have Write Buffer Abort DQ1 set */

if (WriteBufferProgramming &&

((DQ6_TGL_DQ1_MASK & status_read_1) == DQ6_TGL_DQ1_MASK) )

return DEV_WRITE_BUFFER_ABORT;

/* Checking Timeout condition: Check for all devices that have */

/* DQ6 toggling also have Time Out DQ5 set. */

if ((DQ6_TGL_DQ5_MASK & status_read_1) == DQ6_TGL_DQ5_MASK )

return DEV_EXCEEDED_TIME_LIMITS;

/* No timeout, no WB error */

return DEV_BUSY;

}

else

{

/* no DQ6 toggles on all devices */

/* Checking Erase Suspend condition */

April 14, 2010

Designs_for_GL_Products

11

A pplication

Note

status_read_1 = FLASH_RD(base_addr, offset);

status_read_2 = FLASH_RD(base_addr, offset);

/* Checking Erase Suspend condition */

if ( ((status_read_1 ^ status_read_2) & DQ2_MASK) == 0)

return DEV_NOT_BUSY;

/* All devices DQ2 not toggling */

if (((status_read_1 ^ status_read_2) & DQ2_MASK) == DQ2_MASK)

return DEV_SUSPEND;

/* All devices DQ2 toggling */

else

return DEV_BUSY;

/* Wait for all devices DQ2 toggling */

}

}

else

{

/*............................................................*/

/* Use Status Register Read command to read the status

*/

/* register. This is for GL-R/S devices only

*/

/*............................................................*/

#ifdef STATUS_REG

volatile FLASHDATA status_reg;

wlld_StatusRegReadCmd( base_addr, offset );

Issue status register read command */

status_reg = FLASH_RD(base_addr, offset);

/* read the status register */

/*

if ( (status_reg & DEV_RDY_MASK) != DEV_RDY_MASK

) /* Are all devices done bit 7 is

1 */

return DEV_BUSY ;

if ( status_reg & DEV_ERASE_MASK )

return DEV_ERASE_ERROR;

/* Any erase error */

if ( status_reg & DEV_PROGRAM_MASK )/* Any program error */

return DEV_PROGRAM_ERROR;

if ( status_reg & DEV_SEC_LOCK_MASK )/* Any sector lock error */

return DEV_SECTOR_LOCK;

return DEV_NOT_BUSY ;

#endif

return DEV_STATUS_UNKNOWN;

/* should never get here */

}

}

3.16

Accelerated Programming

The S29GL-R does not support accelerated programming, unlike the S29GL-N and S29GL-P. The maximum

voltage that should be applied to the WP#(/ACC) input is VCC + 0.5 V. The S29GL-N and S29GL-P tolerated

up to 12.5 V on the WP#/ACC input.

The S29GL-S does not support accelerated programming, unlike the S29GL-N and S29GL-P. The maximum

voltage that should be applied to the WP#(/ACC) input is VCC + 0.5 V. The S29GL-N and S29GL-P tolerated

up to 12.5 V on the WP#/ACC input.

12

Designs_for_GL_Products

April 14, 2010

Ap pl ic atio n

3.17

No t e

Single Word and Multi-pass Write Buffer Programming

The S29GL-R will not support the single word program command and will only support single pass

programming of each 16 word aligned page using the write buffer programming command. Up to 32 words

can be programmed concurrently per write buffer program operation. This restriction on programming

methods will require system software modification to accommodate.

The S29GL-S will support both single word and write buffer programming commands, consistent with the

S29GL-N and S29GL-P. Unrestricted multi-pass programming is allowed.

4. Power On Reset Timing

The use of a micro controller to perform embedded operations within 65 nm GL Flash requires asymmetric

reset timing. At power on, the flash requires more time in reset to self configure than it does during a warm

reset. Table 4.1 and Figure 4.1 detail the power on reset timing requirements for GL Flash Table 4.2 and

Figure 4.2 detail the warm reset timing requirements for existing and future GL Flash.

Table 4.1 Power On Reset Timing Requirements

Parameter

Description

GL-N

tVCS

VCC Setup Time to first access (min)

tVIOS

VIO Setup Time to first access (min)

GL-P

GL-R

GL-S

50 µs

35 µs

300 µs

300 µs

35 µs

35 µs

300 µs

300 µs

tRPH

RESET# Low to CE# Low (min)

550 ns

35 µs

35 µs

35 µs

tRP

RESET# Low to RESET# High (min)

500 ns

35 µs

200 ns

200 ns

tRH

RESET# High to CE# Low (min)

50 ns

200 ns

200 ns

50 ns

GL-R

GL-S

Note:

For GL-R & GL-S, tRP + tRH must be not be less than tRPH

Figure 4.1 Power-Up Reset Timing

VCC

tVIOS

VIO

tVCS

tRP

RESET#

tRH

tRPH

CE#

Note

The sum of tRP & tRH must be equal to or greater than tRPH

Table 4.2 Warm Reset Timing Requirements

Parameter

Description

GL-N

GL-P

tRPH

RESET# Low to CE# Low (min)

20 µs

35 µs

35 µs

35 µs

tRP

RESET# Low to RESET# High (min)

500 ns

35 µs

200 ns

200 ns

tRH

RESET# High to CE# Low (min)

50 ns

200 ns

200 ns

50 ns

Notes:

1. For GL-N, tRP = 20 µs during embedded operation and 500ns not during embedded operation.

2. For GL-R & GL-S, tRP + tRH must be not be less than tRPH.

April 14, 2010

Designs_for_GL_Products

13

A pplication

Note

Figure 4.2 Warm Reset Timing

tRP

RESET#

tRH

tRPH

CE#

Note:

The sum of tRP & tRH must be equal to or greater than tRPH

5. Specification Parameter Comparison

Table 5.1 provides a side by side reference of various AC and DC specification differences between GL

families (less reset timing requirements). All parameters should be reviewed against actual application

implementations to ensure successful migration. Special attention should be given to review of control signal

relationships during write cycles as well as software suspend & resume timing when evaluating migration to

the S29GL-S family.

Table 5.1 AC and DC Specification Differences (Sheet 1 of 2)

Parameter

Description

GL-N

GL-P

GL-R

GL-S

Read Cycle Time (512 Mbit, VCC=VIO) (min)

100 ns

100 ns

100 ns

90 ns

Intra-Page Access Time (min)

25 ns

25 ns

25 ns

20 ns

Async Read

tACC / tCE

tPACC

tOE

OE# to data (max)

25 ns

25 ns

25 ns

25 ns

tDF

Control negate to data high-Z (max)

20 ns

20 ns

15 ns

15 ns (1)

tWC

Write Cycle Time (512 Mbit, VCC=VIO) (min)

100 ns

100 ns

100 ns

60 ns

tWP

WE# Enable to Disable (min)

35 ns

35 ns

35 ns

25 ns

tWPH

WE# Disable to Enable (min)

30 ns

30 ns

30 ns

20 ns

Datas Setup to WE# Disable (min)

45 ns

30 ns

45 ns

15 ns

WE# Disable to Address (min)

0 ns

0 ns

30 ns (2)

30 ns

tESL

Erase - Suspend to Resume (max)

0 ns

20 µs

30 µs

35 µs

tERS

Erase - Resume to Suspend (typ)

0 ns

0 ns

50 µs (3)

100 µs (3)

tPSL

Program - Suspend to Resume (max)

0 ns

15 µs

30 µs

35 µs

tPRS

Program - Resume to Suspend (typ)

0 ns

0 ns

75 µs (3)

100 µs (3)

Async Write

tDS

tSR/W

Suspend Resume

Throughput

x16 Async Read (512 Mbit, VCC=VIO) (max)

20 MB/s

18 MB/s

20 MB/s

20 MB/s

x16 Page Read (512 Mbit, VCC=VIO) (max)

58 MB/s

56 MB/s

67 MB/s

82 MB/s

Programming (typical)

133 KB/s

133 KB/s

133 KB/s

1.5 MB/s

Erase (typical)

256 KB/s

256 KB/s

256 KB/s

700 KB/s

55 mA

45 mA

60 mA

Power Usage

14

ICC1

Active VCC Read (5 MHz, max)

50 mA

90 mA

90 mA

95 mA

100 mA

5 µA

500 µA

500 µA

20 mA

90 mA

80 mA

N/A

N/A

ICC3

Active Program or Erase (max)

ICC5

Reset Current (max)

IACC

Accelerate Program Current_VCC (max)

Designs_for_GL_Products

April 14, 2010

Ap pl ic atio n

No t e

Table 5.1 AC and DC Specification Differences (Sheet 2 of 2)

Parameter

Description

GL-N

GL-P

GL-R

GL-S

IACC

Accelerate Program Current_WP#/ACC (max)

20 mA

20 mA

N/A

N/A

VHH

WP#/ACC Input - Accelerated Program

Voltage (max)

12.5 V

12.5 V

N/A

N/A

Notes:

1. For GL-S, tDF = 15 ns when VIO = VCC, otherwise, tDF = 20 ns

2. The tSR/W timing parameter only applies in the usage case where CE# is maintained low between a write cycle and a subsequent read

cycle. In this case, an Address change must be delayed for 30 ns minimum from the rising edge of WE# or the data output on the

subsequent read cycle may be incorrect.

3. The minimum tERS and tPRS are 60 ns; however, the stated typical values are necessary for the embedded operations to progress to

completion.

April 14, 2010

Designs_for_GL_Products

15

A pplication

Note

6. Revision History

Section

Description

Revision 01 (February 14, 2008)

Initial Release

Revision 02 (May 22, 2008)

GL Family Feature Comparison

Updated GL Family Feature Comparison table

Feature Difference Discussion

Added Sector Size and Data Size sections

Revision 03 (December 18, 2008)

Packaging

Specification Parameter Comparison

Removed sections Automatic Cache Line and Bit Field Programming

Updated Packaging section

Updated AC and DC Specification Differences table

Revision 04 (September 17, 2009)

Global

General updates

Revision 05 (April 14, 2010)

Global

16

General updates

Designs_for_GL_Products

April 14, 2010

App l ic atio n

No t e

Colophon

The products described in this document are designed, developed and manufactured as contemplated for general use, including without

limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as

contemplated (1) for any use that includes fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the

public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility,

aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for

any use where chance of failure is intolerable (i.e., submersible repeater and artificial satellite). Please note that Spansion will not be liable to

you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products. Any semiconductor

devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design

measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal

operating conditions. If any products described in this document represent goods or technologies subject to certain restrictions on export under

the Foreign Exchange and Foreign Trade Law of Japan, the US Export Administration Regulations or the applicable laws of any other country,

the prior authorization by the respective government entity will be required for export of those products.

Trademarks and Notice

The contents of this document are subject to change without notice. This document may contain information on a Spansion product under

development by Spansion. Spansion reserves the right to change or discontinue work on any product without notice. The information in this

document is provided as is without warranty or guarantee of any kind as to its accuracy, completeness, operability, fitness for particular purpose,

merchantability, non-infringement of third-party rights, or any other warranty, express, implied, or statutory. Spansion assumes no liability for any

damages of any kind arising out of the use of the information in this document.

Copyright © 2008-2010 Spansion Inc. All rights reserved. Spansion®, the Spansion Logo, MirrorBit®, MirrorBit® Eclipse™, ORNAND™,

EcoRAM™ and combinations thereof, are trademarks and registered trademarks of Spansion LLC in the United States and other countries.

Other names used are for informational purposes only and may be trademarks of their respective owners.

April 14, 2010

Designs_for_GL_Products

17

© Copyright 2026