Sample-Rate Conversion: Algorithms and VLSI Implementation

Diss. ETH No. 10980

Sample-Rate Conversion:

Algorithms and VLSI

Implementation

A dissertation submitted to the

SWISS FEDERAL INSTITUTE OF TECHNOLOGY

ZURICH

for the degree of

Doctor of technical sciences

presented by

FRITZ MARKUS ROTHACHER

Dipl. El.-Ing.

born 24. 8. 1965

citizen of Blumenstein BE

accepted on the recommendation of

Prof. Dr. W. Fichtner, examiner

Prof. Dr. W. Guggenb¨uhl, co-examiner

1995

Acknowledgements

I would like to thank my adviser, Prof. W. Fichtner, for his confidence in me

and my work and for establishing a generous working environment. I enjoyed

working at the Integrated Systems Laboratory over the last four years.

I am grateful to my associate advisor, Prof. W. Guggenb¨uhl, for reading

and commenting on my thesis.

I want to thank Gunnar Lehtinen, Andreas Steiner, Dominique M¨uller, and

Christian Siegrist for their effort in implementing the sample-rate converter

during their semester and diploma theses.

I would also like to thank the staff of the Integrated Systems Lab: All secretaries for handling the administrative work, Hanspeter Mathys and Hansj¨org

Gisler for maintaining the logistics, the system administrators Christoph Wicki

and Adam Feigin who fixed all computer-related problems, and Hubert Kaeslin

and Andreas Wieland of the Microelectronics Design Center for their support

concerning VLSI design methodology and tools.

My special thanks go to Norbert Felber, who contributed many valuable

ideas and support in the hardware lab. He found always time and was interested

to discuss digital signal processing and related topics, and offered competent

advice. I owe most of my knowledge of real-world measurement techniques

to him.

Tom Heynemann, Robert Rogenmoser, Hubert Kaeslin, and Nobert Felber

improved the quality of this text by their constructive proofreading.

This work would not have been possible without the support and encouragement of many people outside the ETH. In particular I would like to thank

my parents for their tolerance and support.

i

Contents

Acknowledgements

i

Abstract

ix

Zusammenfassung

xi

1 Introduction

1

:::::::::

Concept : : : : : : : : : :

Related Work : : : : : : :

Structure of the Thesis : :

1.1 Motivation

1.2

1.3

1.4

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

2 Principle in Time and Frequency Domain

::::::::::

Interpolation : : : : : : : : : : : : : : : : : : :

Decimation : : : : : : : : : : : : : : : : : : :

Sample-rate Conversion for Fixed Ratios : :

Sample-rate Conversion for Rational M/L : :

2.1 Test Signals and Sampling

2.2

2.3

2.4

2.5

1

2

4

5

7

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

8

10

11

12

15

iii

:::::::::::::::::::

2.5.2 Downmode : : : : : : : : : : : : : : : : :

2.5.3 Continuous Mode : : : : : : : : : : : : :

Sample-rate Conversion for Any Arbitrary Ratio :

2.5.1 Upmode

2.6

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

3 High-Order Digital Filters

:

3.1.1 Transition Band : : : : : :

3.1.2 Stopband : : : : : : : : :

Realization Considerations : : :

3.2

3.3

3.4

3.5

16

18

19

23

:

:

:

:

FIR Filter and Hold Operation :

:

:

:

:

3.2.1

:

3.2.2 FIR Filter and Lagrange Interpolation

:

3.2.3 Alternatives : : : : : : : : : : : : : : : :

Required Resources : : : : : : : : : : : : : : :

Synthesis of High-Order FIR Filters : : : : : : :

3.4.1 Specifications : : : : : : : : : : : : : : :

3.4.2 Design Technique : : : : : : : : : : : :

3.4.3 Direct Synthesis : : : : : : : : : : : : :

3.4.4 Prototype Method : : : : : : : : : : : :

3.4.5 Relaxed Specifications : : : : : : : : :

Quantization of Filter Coefficients : : : : : : : :

3.5.1 Quantization of FIR Coefficients : : : :

3.5.2 Quantization of Interpolated Coefficients :

3.1 Required Filter Characteristics

15

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

23

24

24

26

26

27

34

36

38

38

39

40

40

43

45

45

47

4 Frequency Tracking

51

:::::::::::

Principle : : : : : : : : : : : : : :

Frequency Counter : : : : : : : :

Digital Phase Locked Loop : : :

4.4.1 Phase Detector : : : : : :

4.4.2 Loop Filter : : : : : : : :

Non-uniform Resampling : : : :

Performance Comparison : : : :

4.6.1 Frequency Counter : : :

4.6.2 Digital PLL : : : : : : : :

4.1 Requirements

4.2

4.3

4.4

4.5

4.6

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

5 Implementation

:::::

5.1.1 Frequency Counter :

5.1.2 Digital PLL : : : : : :

Datapath for FIR Filter : : : :

5.2

5.3

5.4

52

53

55

56

57

58

62

62

65

67

:

:

:

:

5.2.1 Review of Operations

:

5.2.2 Finite Word-Length in Datapath :

DSP Realization Considerations : : : :

ASIC Realization : : : : : : : : : : : : :

5.4.1 Implementation : : : : : : : : : :

5.4.2 Discussion : : : : : : : : : : : :

5.1 Frequency Tracking

51

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

68

68

69

71

71

73

75

77

77

79

6 Measurement Principle & Setup

83

:::::::::::::::::::

Analyzer : : : : : : : : : : : : : : : : : : : :

6.2.1 Frequency Matching for the FFT : :

6.2.2 Windowing for the FFT : : : : : : :

6.2.3 Complex Windows : : : : : : : : : :

Measurement Procedure : : : : : : : : : :

6.1 Generator

6.2

6.3

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

7 Results

:

7.1.2 Digital PLL : : : : : :

System Measurements : : :

Discussion : : : : : : : : : :

7.1.1 Frequency Counter

7.3

85

86

86

89

89

93

7.1 Frequency Tracking Measurements

7.2

83

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

94

95

95

98

103

8 Conclusions

107

A List of Symbols and Integrals

111

B Error Caused by Hold Effect

113

:::::::::::::::::::::::::

White Noise : : : : : : : : : : : : : : : : : : : : : : : : :

Pink Noise : : : : : : : : : : : : : : : : : : : : : : : : :

B.1 Sine Wave

113

B.2

114

B.3

C Error Caused by Linear Interpolation

C.1 Sine Wave

:::::::::::::::::::::::::

114

117

117

C.2 White Noise

C.3 Pink Noise

:::::::::::::::::::::::::

:::::::::::::::::::::::::

118

118

D Performance Measurements

121

List of Figures

146

List of Tables

147

Curriculum Vitae

149

Bibliography

154

Abstract

Many modern signal processing tasks are performed in the digital domain.

Various sample rates are used depending on the required signal quality and

the available bandwidth. Sample-rate conversion is therefore inevitable to

interface systems with different sample rates. In this thesis the concept of

digital sample-rate conversion by integer ratios is extended to arbitrary ratios

and the trade-offs of various design parameters for audio applications are

discussed.

Conceptually, the source samples are interpolated to a heavily oversampled

intermediate signal using a high-order digital filter. To allow a conversion

between arbitrary sample rates this intermediate signal is transformed into a

pseudo-analog representation by holding the value in-between the interpolated

samples. The resulting continuous-time signal is then resampled at the sink

sample rate.

For an infinite interpolation factor, ideal filters, and jitter-free sampling

clocks digital sample-rate conversion is lossless. In this thesis the error contributions of the various non-idealities are quantified. The synthesis of high-order

(> 20000) narrow-band lowpass filters and their quantization properties are

discussed. A digital PLL is presented, which allows to measure precisely the

sink sampling moment relative to the source samples, while attenuating jitter

of the sampling clocks. The effects of the non-uniform sampling due to clock

jitter are treated.

An ASIC for fully digital sample-rate conversion has been developed,

fabricated, and characterized using an all-digital measurement system. A new

(complex) window technique for the FFT is introduced, which minimizes the

window side effects when doing spectrum analysis of multirate discrete-time

signals. Based on the results of this thesis, the design parameters for a converter

with full 20-bit quality are proposed.

ix

Zusammenfassung

Viele moderne Signalverarbeitungsaufgaben werden im digitalen Bereich gel¨ost. Abh¨angig von der geforderten Signalqualit¨at und der verf¨ugbaren Bandbreite werden unterschiedliche Abtastraten verwendet. Abtastratenwandlung

ist daher unumg¨anglich, um Systeme mit unterschiedlichen Abtastraten zu

verbinden. In dieser Doktorarbeit werden die Konzepte f¨ur die digitale Abtastratenwandlung von ganzzahligen zu beliebigen Verh¨altnissen erweitert.

In Abh¨angigkeit von verschiedenen Parametern wird die Qualit¨at und der

Aufwand bez¨uglich Audioanwendungen untersucht.

Vom Prinzip her werden die Eingangswerte zu einem stark u¨ berabgetasteten Zwischensignal interpoliert unter Verwendung eines digitalen Filters hoher Ordnung. Um eine Wandlung zwischen beliebigen Abtastraten zu

erm¨oglichen, wird dieses Zwischensignal in eine pseudo-analoge Darstellung

gewandelt. Dazu wird der Wert des Zwischensignals zwischen zwei Abtastwerten gehalten. Das resultierende zeitkontinuierliche Signal wird danach mit

dem Ausgangstakt neu abgetastet.

F¨ur einen unendlich grossen Interpolationsfaktor, ideale Filter und jitterfreie Taktsignale ist die digitale Abtastratenwandlung verlustlos. In dieser

Doktorarbeit werden die Fehleranteile von verschiedenen Nichtidealit¨aten

abgesch¨atzt. Die Synthese von schmalbandigen Tiefpassfiltern hoher Ordnung (> 20000) und deren Eigenschaften f¨ur begrenzte Wortl¨angen werden

behandelt. Ein digitaler PLL wird vorgestellt, welcher die Abtastzeitpunkte

am Ausgang relativ zum Eingangstakt sehr genau misst und gleichzeitig Jitter

der Taktsignale d¨ampft. Die durch Taktjitter verursachten Auswirkungen von

nicht a¨ quidistanten Abtastzeitpunkten werden ebenso besprochen.

Ein ASIC f¨ur ausschliesslich digitale Abtastratenwandlung wurde entwickelt, hergestellt und mit einem vollst¨andig digitalen Messystem ausgemessen.

F¨ur die Spektralanalyse von zeitdiskreten Signalen mit mehreren Abtastraten

xi

wird eine neue (komplexe) Fenstertechnik f¨ur die FFT verwendet, welche die

Nebeneffekte des Fensters auf ein Minimum reduziert. Ausgehend von den

Resultaten dieser Doktorarbeit werden die Parameter f¨ur einen Wandler mit

voller 20-bit Qualit¨at vorgeschlagen.

1

Introduction

1.1

Motivation

Modern signal processing problems are often solved in the digital domain

due to the availability of powerful VLSI circuits which allow to perform

complex operations in real-time, without the well-known shortcomings of

analog implementations. The source signal is transformed into the digital

domain by an A/D converter. All data processing, e.g. filtering, shaping,

mixing etc., is done in the digital domain and only the final result is converted

back to analog. To overcome the degradation caused by successive A/D-D/A

conversion, all processing blocks must have digital interfaces.

Depending on the available bandwidth of the channel, the required quality,

and the data rate of the interfaces a wide variety of sample rates are used:

e.g. 48 kHz for professional digital audio systems, 44.1 kHz for consumer

digital audio (CD), 32 kHz for digital satellite radio (DSR), or 44.056 kHz for

video compatibility (VCR). The incorporation of all these systems is however

trouble-free, if a sample-rate converter is used at each interface.

Sample-rate conversion is also used in the growing field of digital audio

compression systems. Downsampling followed by data compression allows

transmission of a high-quality audio signal over a 64 kbit/s ISDN telephone

line [dGL94].

1

From source to sink, signals are repeatedly converted for editing, storage,

and transmission. To retain the signal quality of the original recording –

even after several cascaded converters – the conversion must be virtually

transparent.

1.2

Concept

Many digital signal processing applications necessitate a conversion of the

sample rate at the interface to match it to the following system. Conceptually, sample-rate conversion by non-rational ratios is accomplished in the

digital domain by interpolating the incoming samples to a high enough sampling frequency (usually in the GHz range) and subsequently decimating this

oversampled data to the target sample rate by choosing the appropriate samples. Practically the problem will be partitioned into a frequency tracking unit,

which determines precisely the sink phase relative to the source samples, and

into a high-order digital interpolation/decimation filter. This filter limits the

signal either to half the source or to half the sink sample rate to avoid aliasing.

Therefore two different modes of operation result depending on whether the

source or the sink sample rate is larger.

Research activities of our laboratory demonstrated a way to overcome the

need for two separate modes for up- and downsampling: The cutoff frequency

of the interpolation/decimation filter is dynamically adjusted – according to the

ratio of sink and source sample rate – by using the frequency scaling property

of the Fourier transform. We call this capability for a smooth transition

between up- and downsampling CONTINUOUS MODE [RW90]. Based on the

CONTINUOUS MODE we proposed and realized a VLSI architecture of a samplerate converter for arbitrary ratios [LS91]. We will refer to this implementation

as SARCO (SAmple-Rate COnverter).

For the interpolation/decimation filter, the precise ratio of the source and

the sink sample rates must be measured. If both sample rates are synchronous

i.e. derived from the same master clock and if this master clock is available,

both rates can be measured by a counter running with the master clock. If the

master clock is not available, it can be recovered by means of a phase-locked

loop (PLL), which additionally suppresses clock jitter. A buffer (FIFO) is then

used for the data exchange. However, non-synchronous interfaces require a

new solution.

In general three cases can be distinguished:

A. Synchronous Interfaces

B. Plesiochronous Interfaces

C. Asynchronous Interfaces

Synchronous interfaces are the easiest to handle (as shown above), but

real-world problems are often plesiochronous or asynchronous. In the plesiochronous case two systems may have the same nominal sample rates, but

due to tolerances or temperature drift of the two independent oscillators, the

two frequencies are not phase-locked, but differ by a small, varying amount e.g.

in the range of 100 ppm. Asynchronous interfaces apply for examples where

sources of different independent sample rates are to be mixed or equipment

with arbitrary sample rates has to be connected.

The frequency measurement can be realized accurately by several methods:

1. Measurement performed with a very high-frequency clock (GHz)

2. Averaging measurements performed with a medium-frequency clock

3. Determination of the precise sample phase by a (digital) phase-locked

loop

For dynamically changing sample rates an optimal trade-off between precise tracking and noise suppression must be found. High-frequency measurement allows to follow sample-rate changes immediately. Unfortunately jitter

of the sampling frequencies is not suppressed in this case, but modulated onto

the audio signal. The lowpass filters used for systems of type 2 and 3 remove

high frequency noise at the cost of slower tracking.

In this thesis the emphasis is put on a unified approach to the implementation of sample-rate conversion of audio signals with arbitrarily changing ratios.

The effects of non-ideal filtering and non-uniform sampling are analyzed and

their effect on the signal quality is discussed. Additionally, considerations

on VLSI implementation are presented. This field of research involves a

large number of digital signal processing topics, including high-order filter

synthesis, digital phase-locked loops (DPLL), real-time filtering, time-varying

and adaptive filters, polyphase structures, finite word-length effects, spectrum

analysis, and VLSI architecture.

1.3

Related Work

The simplest solution for sample-rate conversion in the digital domain is to

repeat or omit a sample from time to time to match the sample rates. This

method is especially applicable for plesiochronous sample rates, but yields

only low quality results. In professional applications the problem of samplerate conversion by arbitrary ratios is often reduced to the synchronous case

by equipping all external sources, such as CD players or DAT machines, with

a synchronization input. The speed of the external source is then adapted

according to the system master clock.

The basic operations for synchronous sample-rate conversion (type A)

from a signal processing point of view have been covered in [CR81]. [LK81,

LPW82] extended this work to non-rational ratios,but distinguished two modes

depending on whether the sink sample rate is larger or smaller than the source

rate. Plesiochronous interfaces (type B) cannot be realized with this distinction

without smooth switching between modes. A first hardware implementation

has been realized following the above principles, which required some 400

integrated circuits per audio channel [Lag82]. In 1983 a theoretical exposition

of many aspects of multirate digital signal processing appeared in [CR83]. It

treats the advantages and disadvantages of FIR and IIR filters for interpolation

and decimation by rational ratios in detail and gives many design examples.

These realizations all have the disadvantage that they are not well suited for

the CONTINUOUS MODE, but only for fixed sample-rate ratios. [CR83] also

covered the realization of high-order filters by cascading several low-order

stages, which are easier to realize. [Ram84] discussed how to reduce the

storage requirements for the filter coefficients by using various interpolation

methods.

Most publications on sample-rate conversion do not cover in depth the

need for proper frequency tracking although this is crucial for high quality

audio applications. [LPW82] suggested the use of a moving average filter

for frequency tracking. [Sti92] used a digital PLL running at a multiple of

either the source or the sink sample rate. Frequency measurement with a

GHz counter has not jet been realized due to the lack of jitter suppression and

technology limitations.

In addition to the prototype hardware implementation mentioned above,

several sample-rate converters have been realized using general purpose digital signal processors. [PHR91] implemented a sample-rate converter on a

DSP56001. The interpolation/decimation filter has been realized by multiplying a SINC function by the Blackman-Harris window function, as suggested

by [Ram82]. [CDPS91] realized a sample-rate converter between 44.1 kHz

and 48.0 kHz using B-splines. A two stage FIR interpolation each by a factor

2 is followed by a 6th order B-spline interpolation. However, these implementations are limited to fixed sample-rate ratios.

The first commercial VLSI implementation of a sample-rate converter using the CONTINUOUS MODE has appeared recently [AK93]. A second commercial realization of a sample-rate converter by [JTG+ 94] follows an alternative

approach, which will be discussed briefly.

1.4

Structure of the Thesis

This thesis describes theory, experience, and results that have been gained

during the development and test of an application specific integrated circuit

(ASIC) for sample-rate conversion of audio signals with arbitrarily changing ratios. In particular the error contribution of various non-idealities are

discussed and the parameters for a true 20-bit converter are derived.

In Chapter 2 an overview of the basic principle for sample-rate conversion

in the digital domain is given. The well-known concepts of interpolation and

decimation by integer factors are applied to sample-rate conversion by rational

ratios. The CONTINUOUS MODE already published by the author in [RW90],

which extends the sample-rate conversion to arbitrary sample-rate ratios, is

described in detail.

Chapter 3 gives insight into the strategies for the design and synthesis of

very high-order (> 20 000) narrow-band lowpass filters. Several one- and

multistage implementations are compared in performance, implementation

cost, and required computation power. An interpolation method which reduces

the storage requirements for the filter coefficients is presented. Additionally,

the effects of filter coefficient quantization on the transfer function is discussed.

Chapter 4 compares several alternatives for the realization of the frequency tracking unit. The performance and cost of high-frequency measurement,

averaged medium-frequency measurement, and a digital PLL are compared

for synchronous, plesiochronous and asynchronous sampling frequencies. In

addition the effects of non-uniform (jittered) sampling are discussed.

Chapter 5 evaluates the system complexity and compares ASIC and DSP

implementations according to hardware requirements and costs.

In Chapter 6 the measurement principles for multirate digital audio systems

and the hardware setup used for the measurements in this thesis are presented.

A new window technique for the FFT is introduced, which allows to minimize

the side effects of the window when doing spectrum analysis of multirate

discrete-time signals.

Chapter 7 compares the different concepts, architectures and implementations by measurements.

2

Principle in Time and Frequency

Domain

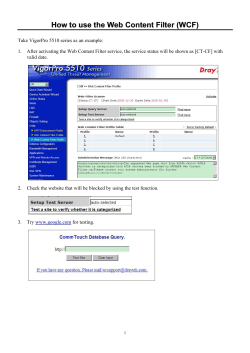

The obvious method to transfer an audio signal between unassociated sample

rates is digital-to-analog (D/A) conversion followed by analog-to-digital (A/D)

conversion (Fig. 2.1).

D/A

DA-ADconv.epsi

f source 103 21 mm

f source

Reconstruction

Filter

A/D

f sink

Anti-aliasing

Filter

f sink

Figure 2.1: D/A conversion followed by A/D conversion

This method works for any ratio of sink sample rate fsink to source sample

rate fsource , but is tainted with several limitations. First of all, to retain the

large signal-to-noise ratio (S/N) of a digital audio signal expensive high-quality

D/A and A/D converters have to be used. Secondly, the output signal of the

D/A converter must be reconstructed by an analog filter of high precision

with cutoff frequency fsource =2. Additionally, to fulfill the Nyquist theorem,

the input signal of the A/D converter must be band-limited to fsink =2 by an

anti-aliasing filter.

If the sink sample rate fsink is larger than the source sample rate fsource

7

– we will refer to this case as UPMODE– the second filter can be omitted. In

the opposite case (DOWNMODE) the first filter is not necessary. Therefore both

lowpass filters can be merged into one with cutoff frequency

fcutoff =

fsource if f

sink > fsource UPMODE

2

fsink

otherwise

DOWNMODE

(2.1)

2

This reconstruction/anti-aliasing filter, which must be realized in the analog

domain, needs a flat passband, a narrow transition band and a highly attenuated

stopband. The required specifications for 16 bit quality make the problem

hardly solvable.

A third disadvantage of the D/A-A/D approach is – besides the need for

high-quality D/A and A/D converters and the expensive analog filter – that

any jitter on the sampling clocks will translate into signal distortion and thus

needs to be suppressed by additional circuitry.

We can avoid many of the above problems by performing the sample-rate

conversion process in the digital domain. The A/D and D/A converters are

omitted and the analog filters are replaced by digital ones. This concept will

be explained in detail in the following sections.

2.1

Test Signals and Sampling

The spectrum of the example signal that is used for illustrative purposes

throughout this thesis is shown in Figure 2.2.

X(f)

Signal.epsi

49 31 mm

1

2

⋅f sample

f sample

f

Figure 2.2: Spectrum of example signal

It is composed of three parts: a low-frequency sine wave, a high-frequency

sine wave and a third component, which declines linearly with the frequency.

This third component shall represent the spectrum of a typical audio signal,

while the first two show the response for low- and high-frequency components.

For noise calculations three sine waves at 1; 10; 20 kHz, white noise, and

pink noise are used as test signals. White noise is a random signal, which has

an equal amount of energy per Hertz of bandwidth. Pink noise however is

random noise delivering an equal energy per octave [Ben88]. This distribution

matches more precisely the sensitivity of the ear. Figure 2.3 shows the spectral

power density of pink noise and white noise respectively.

S(f) [dB/Hz]

-20.8

Pink.epsi

101 33 mm

-30.8

-40.8

-46.0

-50.8

20

200

2 000

20 000 f [Hz]

Figure 2.3: Pink noise S (f ) = 61f , white noise S (f ) = ∆1f

The well-known sampling theorem states that a continuous-time signal x(t),

with a spectrum X(f) that is band-limited to fsample =2, can be uniquely and

error-free reconstructed from its samples x[n]. The spectrum of these samples

is composed of the original spectrum X(f), which repeats at all multiples of the

sampling frequency (Fig. 2.4). If the analog signal x(t) contains components

at frequencies higher than fsample =2 they will distort the sampled signal in the

form of spectral fold-over (aliasing) and can not be recovered anymore.

baseband

Sampling.epsi

99 18 mm

f sample

2⋅f sample

3⋅f sample

4⋅f sample

5⋅f sample

Figure 2.4: Spectrum of a sampled signal with sample rate fsample

A second parameter – besides the sampling frequency – which characterizes the sampled data is the word-length used to represent the data samples.

The effects of finite word-length will be neglected in the following sections,

but will be discussed in Sections 3.5 and 5.2.2.

2.2

Interpolation

In this section the increase of the sample rate by an integer factor L is described.

In the following we refer to this process as interpolation.

f sample

L⋅f sample

Interpolation.epsi

99 37 mm

HL

L⋅f sample

f sample

Figure 2.5: Interpolation by a factor L

If we increase the sample rate of a signal we can preserve the full signal

content according to the sampling theorem. After the interpolation the signal

spectrum repeats only at multiples of the new sample rate L fsample (Fig. 2.5).

The interpolation is accomplished by inserting L-1 zeros between successive

samples (zero-padding) and using an (ideal) lowpass filter with

(

HL (f ) =

L

0

f

for 0 < f < sample

2

f

for sample

<

f

< Lfsample

2

2

(2.2)

The multiplication of a signal with spectrum X (f ) with a transfer function

H (f ) in frequency domain Y (f ) = H (f ) X (f ) corresponds to a convolution

of the signal in the time domain y (t) = h(t) ? x(t). For the zero-padded

discrete-time signal x[.] we get

+1

X

k

y[m] =

hL [m , k] x L ;

k=,1

for k

=

L; 2L; 3L; : : :

(2.3)

If we substitute k by (m div L) L , n L we get

y[m]

=

=

+1

X

n=,1

+1

X

n=,1

hL m , (m div L) L + n L x [m div L , n]

(2.4)

hL [n L + m mod L] x [m div L , n]

(2.5)

where m div L is the integer portion of the division m=L , and m mod L

denotes the remainder.

For each output value y [m] we therefore multiply and accumulate n samples of the impulse response hL [:] by the corresponding input samples x[:].

Note that the samples of the impulse response hL[:] are equidistant with spacing

L.

2.3

Decimation

To decrease the sample rate by an integer factor M (decimation) we must

first band-limit the signal to fsample =(2 M ) (Fig. 2.6) by the lowpass filter

HM (Eq. 2.6) to comply with the sampling theorem and keep only every Mth

sample. As a result, we loose all signal content above half the target sampling

frequency fs =M .

HM

1/M⋅f sample

Decimation.epsi

104 38 mm

1/M⋅f sample

Figure 2.6: Decimation by a factor M

f sample

f sample

(

HM (f ) =

1

0

f

for 0 < f < sample

2M

f

f

sample

for 2M < f < sample

2

(2.6)

To get the decimated signal we start from an initial phase '0 , which can

be chosen arbitrarily, keep every Mth sample and skip all other samples

(Eq.2.7). There exist therefore M different sets of samples (depending on the

initial phase '0 ), which all represent the same signal.

y[m] =

2.4

+1

X

n=,1

hM [m M + '0 , n] x [n] ;

for '0

=

0; : : : ; M

,1

(2.7)

Sample-rate Conversion for Fixed Ratios

In the preceding section we have considered interpolation and decimation as

two separate operations. To perform sample-rate conversion by a fixed ratio

M=L these two operations have to be cascaded (Fig. 2.7). Note that the

interpolation must precede the decimation to keep the maximum bandwidth of

the source signal.

L

HM

HL

M

Conversion.epsi

103 38 mm

f source

L⋅f source

L⋅f source

f sink

L/M⋅f source = f sink

Figure 2.7: Sample-rate conversion by a fixed ratio M=L

The two lowpass filters can be merged into a single one with a cutoff

frequency, which is half of the minimum of source and sink sample rate

(Eq. 2.8).

HLM (f ) =

L

0

for 0 < f < min( fsource

; fsink

2

2 )

otherwise

(2.8)

The interpolation of the source signal by the factor L is succeeded by

the decimation of factor M . Therefore, instead of calculating the interpolated

signal at the rate L fsource and keeping only every Mth value, we can operate

the interpolation/decimation filter at the rate L=M fsource , as indicated by the

dotted line in Figure 2.7, but we must choose the correct set of filter coefficients

for each sink sample.

If we substitute m in Equation 2.5 by 'sink [m] = m M + '0 (Eq. 2.7)

we obtain the formula for sample-rate conversion by fixed integer ratios

y[m] =

+1

X

j =,1

hLM j L + 'sink [m] mod L x 'sink [m] div L , j

(2.9)

with

'sink [m] = m M + '0 ;

mod

Modulo division;

div

Integer division

This is the all-digital equivalent to the D/A-A/D solution (Fig. 2.1, Eq. 2.1),

if we use a infinitely large interpolation factor L.

The theoretical concept for sample-rate conversion by fixed integer ratios

has already been treated in [CR83]. But for an actual realization of Equations 2.8 and 2.9 the following problems are to be solved:

1. Equation 2.8 specifies a lowpass filter with a constant passband gain

and a transition band of width zero. The impulse response of such

a rectangular filter with cutoff frequency fcutoff and a sample rate

L fsample is

h[n] =

f

sin[2n Lcutoff

fsource ]

f

2n Lcutoff

fsource

=

SINC [n 2 fcutoff

L fsource ]

(2.10)

and extends from n = ,1 to n = +1. An actual realization can

only be a high-order lowpass filter of finite length due to the causality

principle. The synthesis problems for such high-order (lowpass) filters

are discussed in Chapter 3. In the following we assume that the filter is

of order Q L + 1 with a sufficiently large Q.

2. For a lossless sample-rate conversion we assumed an infinite stopband

attenuation of the lowpass. A filter of finite length can only reach a

finite stopband attenuation, however. Furthermore the quantization of

the filter coefficients h[:] additionally alters the filter transfer function.

In Chapter 3 we will evaluate the achievable stopband attenuation of

the lowpass h[:] and introduce the concept of quasi-floating-point (QFP)

notation for the filter coefficients. The effects of finite word-length

computation in the datapath are discussed in Section 5.2.

3. The cutoff frequency of the lowpass (Eq. 2.8) is not constant for variable

ratios M=L, but is defined by

fcutoff =

fsource if f

sink > fsource UPMODE

2

fsink

otherwise

DOWNMODE

(2.11)

2

[Pel82] distinguished two modes of operation depending on whether the

sink sample rate is larger or smaller than the source rate. The same

lowpass filter either runs with the source or the sink sample rate and

thereby only one set of filter coefficients is needed. The disadvantage

of this approach is that switching from one mode to the other requires

muting of the output signal. The CONTINUOUS MODE to be presented in

Section 2.5.3 overcomes this limitation.

4. For fixed sample rates M and L can be calculated in a straightforward

manner, e.g. for fsource = 48 kHz and fsink = 44:1 kHz we get M =

160 and L = 147. On the other hand, if the two clock sources are

not synchronous their ratio can be non-rational and may even vary over

time. The sample-rate converter must be able to accept any ratio of sink

and source sample rate. Furthermore it must suppress short-time jitter

of the sampling clocks. The different frequency tracking principles for

arbitrary ratios M=L are described in Chapter 4, whereas in Section 2.6

we will estimate the required interpolation factor L for professional

audio quality.

2.5

Sample-rate Conversion for Rational M/L

In Section 2.4 we treated the sample-rate conversion for fixed ratios and stated

that the cutoff frequency of the interpolation/decimation lowpass must be

either fsource =2 (if fsource < fsink ) or fsink =2 (Eq. 2.11). In this section we

describe how the frequency scaling property of the Fourier transform can be

used to adjust the cutoff frequency of the lowpass filter dynamically to allow

a smooth transition between both modes.

Adaptive Filter

Rational.epsi

103 26 mm

L

f source

M

f sink

L⋅f source

Figure 2.8: Sample-rate conversion by a rational ratio M=L

Note that since M=L is rational all operations can be performed on a

discrete time-grid. The time unit is defined by the source sample rate as

tunit = L f1

(2.12)

source

Using this time unit, the source sample period is L tunit and the sink sample

period is accordingly M tunit .

2.5.1

Upmode

If the sink sample rate is larger than the source sample rate we can preserve

the full bandwidth of the source signal. If we assume filter h to be of order

Q L + 1, using Equation 2.9, we get

y[m] =

Q

+ 2

X

j =, Q2

2

z

}|

sink [ ]

h j L+'

6

4

' m]

∆ [

m

3

2

{

7

5

x '

mod L

z

6

4

with 'sink [m] = m M

+

ptr[m]

}|

sink [ ]

m

'0

3

{

div L ,j 5 (2.13)

7

Figure 2.9 gives a graphical representation of Equation 2.13. Because all

mathematical operations in Equation 2.13 are integer operations, we will stay

on the time-grid defined in Equation 2.12.

ptr[m]

source

samples

L

∆ϕ[m]

ϕ0

sink

samples

ϕ sink

M

Upmode.epsi

104

52 mm

[m]

h [n]

∆ϕ[m] -L+∆ϕ[m]

L+∆ϕ[m] -2⋅L+∆ϕ[m]

Figure 2.9: UPMODE, fsink

> fsource, L > M

Starting from a measured initial phase '0 (on the grid) the phase of the

sink samples 'sink [m] is incremented by M (time units) for every value y [m].

Each value of 'sink [m] determines both the phase of the sink sample relative

to the last source sample ∆'[m] as well as its position ptr [m]. Depending on

the phase difference ∆'[m] one particular subset of the samples of the impulse

response h is taken. The samples of the impulse response have a spacing of L.

Since the lowpass filter h is of order Q L + 1, L different subsets of Q + 1

values exist.

2.5.2

Downmode

If the sink sample rate is smaller than the source sample rate we are not able

to preserve the full frequency range of the source signal, but must limit it to

fsink =2 by the lowpass filter h0 (Eq. 2.11).

Q

+ 2

X

j =, Q2

2

' m]

∆ [

3

2

z

ptr[m]

3

}|

{

}|

{

z

6

7

6

0

h 4j L + 'sink [m] mod L5 x 4'sink [m] div L ,j 75

(2.14)

In order to use the same lowpass filter coefficients as in the UPMODE

(fcutoff = fsource =2) we use the frequency scaling property of the Fourier

transform to alter the cutoff frequency from fsource =2 to fsink =2.

fsink i

h

fsource

fsource

h0[i] = fsink

L h L i

=

M

M

(2.15)

If Equations 2.14 and 2.15 are combined we get for y [m] in the DOWNMODE

2

Q

M

L2

X

3

' m]

∆ [

2

3

ptr[m]

z

}|

{

}|

{

z

L

6L

7

6

7

(j L + 'sink [m] mod L)5 x 4'sink [m] div L ,j 5

h

4

M j=, M Q M

+

L

2

with 'sink [m] = m M

+

'0

L

ptr[m]

source

samples

sink

samples

(2.16)

∆ϕ[m]

ϕ0

M

ϕ sink [m]

Downmode.epsi

108 69 mm

h’[n]

h [n]

∆ϕD[m] -L2/M+∆ϕD[m]

L2/M+∆ϕD[m] -2⋅L2/M+∆ϕD[m]

Figure 2.10: DOWNMODE, fsink

< fsource, L < M

Figure 2.10 illustrates Equation 2.16. The phase 'sink [m] for each sink

sample y [m] is calculated in the same way as in the UPMODE, but the filter

coefficients must be scaled by L=M . The effective phase difference ∆'D [m]

is therefore L=M ('sink [m] mod L) and the samples of the impulse response

have a spacing of L2 =M . Since L=M determines only the cutoff frequency

of the decimation filter we can alter it slightly so that L2 =M is an integer and

stays on the time-grid defined in Equation 2.12.

P

The number of multiplication and accumulations ( x[:] h[:]) increases

from Q + 1 in the UPMODE to Q M=L + 1 in the DOWNMODE.

2.5.3

Continuous Mode

The CONTINUOUS MODE combines both UPMODE and DOWNMODE. Since the

cutoff frequency of the lowpass filter is adapted continually, there is a smooth

transition between both modes.

y[m] = % QD

+ 2

X

j =, QD

h j L % + ∆'D [m] x ptr[m] , j

(2.17)

2

with

'sink [m]

ptr[m]

%

∆'D [m]

QD

UPMODE

DOWNMODE

if L > M

if L < M

i.e. fsink

> fsource i.e. fsink < fsource

m M + '0

'sink [m] div L

1

'sink [m] mod L

Q

L

M

L

M ('sink [m] mod L)

M Q

L

Recall that to stay on the time-grid, % must be altered slightly so that L2 =M

is an integer. Additionally, QD must be rounded up to the next even integer

and the initial phase ∆'D [0] = L=M ' must be rounded to the next integer.

2.6

Sample-rate Conversion for Any Arbitrary

Ratio

Up to now we have assumed that the ratio of source to sink sampling frequency

is a rational number and can consequently be written as M=L. If we choose L

large enough we can approximate any rational number to a sufficient precision.

However there are practical implementation limits for L. In this section we

will estimate the minimum required order of L for 18- and 20-bit quality.

x(t)

y(t)

HoldTime.epsi

107 35 mm

â

x[n]

T=1/(L⋅f source)

Figure 2.11: Continuous-time representation

between samples xˆ [n]

y(t)

by holding value in-

If the source and the sink sample rates have an arbitrary (or even varying)

ratio, we need to change from the discrete time-grid (Eq. 2.12) to a continuoustime representation. This can accomplished by interpolating the source signal

with a large, but fixed interpolation factor L and holding the value in-between

the interpolated samples (Fig. 2.11). This continuous-time signal is then

resampled at the sink sample rate.

Note that instead of holding the sample value between successive samples,

linear or higher order interpolation between samples could be used as well.

However, since the available time-resolution is limited, these operations must

be followed by a hold operation to get a continuous-time signal. We will

discuss this approach further in Chapter 3.

Figure 2.12 shows a block diagram of the required operations using the hold

operation. The source signal x[n] is interpolated to xˆ [n] and then converted

to the continuous-time signal y (t) by the hold operation. y (t) can then be

resampled at any required moment.

The hold operation of the value of the interpolated source signal during the

Adaptive

Filter

L

Continuous

Time

Discrete

Time

Arbitrary.epsi

105

30 mm Hold

â

x[n]

x[n]

f source

Resample

y(t)

y[m]

f sink

L⋅f source

Figure 2.12: Sample-rate conversion by an arbitrary ratio M=L

time T = 1=(L fsource) can be expressed in the time domain as a convolution

of the interpolated samples with a rectangle of width T (Eq. 2.18).

y(t) = xˆ [n] ?

RECT (

1

L fsource )

(2.18)

This convolution in the time domain corresponds to a multiplication with

a SINC function in the frequency domain (Eq. 2.19).

Y (f ) = Xˆ [f ] HHold (f ) = Xˆ [f ] SINC (

f )

L fsource

(2.19)

After interpolation by a factor L the spectrum of the source signal repeats

at all multiples of L fsource . Figure 2.13 shows both the spectrum of the interpolated source signal and the transform of the hold operation. The resulting

spectrum is the multiplication of both.

H Hold

Hold.epsi

103 30 mm

L⋅f source

=

1⋅f i

2⋅L⋅f source

=

2⋅f i

3⋅L⋅f source

=

3⋅f i

Figure 2.13: Interpolation by L and hold operation

The baseband signal up to fsource =2 is left (almost) unchanged by the

hold operation, while all remaining signal components at multiples of fi =

L fsource are attenuated by the SINC . They will be folded back into the

baseband after the decimation. If fsource and fsink are uncorrelated we can

assume that the signal amplitudes of different folding products that are folded

back to the same location in the baseband do neither add nor totally cancel each

other. Therefore their energy can be summed up. The total error power due to

the hold operation for a full-scale signal is listed in Table 2.1 for five different

signals. The derivation of these values can be found in Appendix B. Note that

these errors correspond to full-scale signals, and scale down proportionally for

smaller signal levels.

Sine @ 1 kHz

Sine @ 10 kHz

Sine @ 20 kHz

White Noise

Pink Noise

Error in [dB] for L=

2k

216

218

,28:5 , k 6:02 ,124:8 ,136:9

,8:5 , k 6:02 ,104:8 ,116:9

,2:4 , k 6:02 ,98:7 ,110:8

,8:6 , k 6:02 ,104:9 ,117:0

,13:2 , k 6:02 ,109:5 ,121:6

Table 2.1: Error caused by hold operation (fsource

=

220

,148:9

,128:9

,122:8

,129:0

,133:6

48 kHz)

The largest portion of the error is contributed by the components at the

first zero crossing of the SINC function (Fig. 2.13, f = fi ). If the audio

signal is a sine wave with frequency fsig we get two contributions around fi

at f = L fsource fsig with an amplitude of fsig =(L fsource ) (Eq. B.2).

These two components contain about 60 % of the total error energy due to the

hold effect. I.e. for a 1 kHz (20 kHz) signal sampled at fsource = 48 kHz and

an interpolation factor of L = 216 the two error peaks appear ,5:2 dB below

the value given in Table 2.1 at ,130 dB (,104 dB).

In this section we have calculated the error introduced due to an arbitrary,

non-rational ratio of source and sink sample rate depending on the interpolation

factor and various source signals. Thereby we presumed the sample-rate ratio

and thus the resampling moment to be known precisely. We will discuss

this assumption further in Chapter 4, after the presentation of the frequency

tracking unit.

For performance and cost estimations in the following chapters we will

use two different interpolation factors:

1. For L = 216 18-bit quality can be reached for a pink noise audio signal,

but for full-scale signals close to fsource =2 only 16-bit accuracy is

possible.

2. For L = 220 the sum of all error components is below ,122 dB for all

five signals shown in Table 2.1. 20-bit quality can therefore be achieved

over the full audio bandwidth.

3

High-Order Digital Filters

In Chapter 2 we assumed that the interpolation/decimation lowpass has a constant passband gain, a transition band of width zero, and an infinite stopband

suppression (Eq. 2.8). In this chapter we will estimate the minimally required

filter specifications for professional digital audio applications and discuss various realization methods. Furthermore the quantization properties of high-order

narrow-band lowpass filters are discussed.

As shown in Section 2.5.3, the CONTINUOUS MODE uses the same filter

coefficients for the UPMODE and the DOWNMODE. In the following sections we

will therefore design the filter and estimate the performance for the UPMODE.

We will discuss the implications on the DOWNMODE in Section 3.3.

3.1

Required Filter Characteristics

The interpolation/decimation filter is specified by a passband from 0 to fp with

a ripple smaller than p and a stopband that starts at fs with an attenuation

of at least s (Fig. 3.1).

23

δp

FiniteFilter.epsi

103 32 mm

δs

fp fs

f i = L⋅f source

f source

Figure 3.1: Filter with finite stopband attenuation

3.1.1

Transition Band

The transition band of the filter must be narrow, because signal components

just below fsource =2 must pass unaltered, whereas those just above must be

sufficiently suppressed. For high-quality audio fp = 15=32 fsource and

fs = 17=32 fsource is chosen [Pel82]. Note that the transition band is

symmetric in respect to fsource =2 and will therefore not alias into the baseband

(below fp = 15=32 fsource). Table 3.1 gives the borders of the transition band

for the three most common sampling frequencies. With 48 kHz for example,

the passband extends up to 22.5 kHz.

fsource

fp

fs

48.0 kHz

44.1 kHz

32.0 kHz

22.5 kHz

20.7 kHz

15.0 kHz

25.5 kHz

23.4 kHz

17.0 kHz

Table 3.1: Transition bandwidth for common sampling frequencies

3.1.2

Stopband

In Section 2.3 we stated that the interpolated signal is to be band-limited to

half the target sample rate before the decimation takes place. This requirement

is only approximated by a filter with a finite stopband attenuation s (Fig. 3.1).

The remaining stopband energy (from fsource =2 upwards) of the higher order

images is therefore attenuated by s and is then folded back into the baseband.

The alias error of the residual signals at multiples of fi = L fsource caused

by the hold operation has already been discussed in Section 2.6 (Fig. 2.13,

FilterHold.epsi

103 27 mm

δs

1⋅f i

2⋅f i

3⋅f i

Figure 3.2: Weighted stopband error

Table 2.1). This contribution is not affected by the finite stopband attenuation

and is therefore left blank in Figure 3.2.

As mentioned above, an additional error contribution results from the nonzero stopband which is weighted by the SINC -function of the hold operation

(Fig. 3.2). For a large interpolation factor L the signal energy is approximately

equally distributed over the stopband since the signal spectrum is repeated

many times. If we further assume that the filter has a constant stopband

attenuation s the total stopband energy is obtained by

Estop = 2 1Z

X

j =0

j

fi, fsource

( +1)

2

j fi+ fsource

2

s) f

(

2

source

!2

sin( ffi )

df

ffi

(3.1)

Assuming the same error energy density in the (narrow) passband as in the

stopband right through, Equation 3.1 can be simplified (using Eq. A.2) to

Estop =

Z

1 (s)2

!2

sin( ffi )

df

fsource ffi

2 (s )2 fi

2

= L (s )

fsource 2 2

0

(3.2)

If the error introduced by the finite stopband attenuation should be smaller

than ,110 dB and L = 216 (hold error at ,110 dB for pink noise; Table 2.1)

then s must be less than ,160 dB (Eq. 3.2). For a stopband attenuation of

,130 dB and L = 220 , s must even be below ,190 dB.

3.2

Realization Considerations

In this section we discuss several alternatives for the realization of the interpolation/decimation filter specified in the previous section. In Section 3.2.1

the order and computational cost of a single stage FIR filter is estimated. This

filter is followed by the hold operation and the decimation. In Section 3.2.2

the hold operation is replaced by linear interpolation, allowing a lower order

filter. In Section 3.2.3 alternative implementations are discussed briefly.

3.2.1

FIR Filter and Hold Operation

The most direct implementation is the use of a single stage FIR filter followed

by the hold operation as depicted in Figure 3.3. What is the order of a single

stage FIR filter, which fulfills the specifications given in Section 3.1?

Discrete

Time

Single

Stage SingleStage.epsi Hold

FIR

97 22 mm

L

Continuous

Time

Resample

f sink

f source

Figure 3.3: Single stage FIR filter followed by hold operation

[Rab73] derived an empirical formula to estimate the order of a Chebyshev

lowpass filter for specified p ; s ; fp ; fs . Table 3.2 gives the approximate order

N of the lowpass filter according to this formula for various values of Estop,

L, and p. The parameters s , fp , fs are calculated according to Equation 3.3.

q

1

17 1

;

f

=

s = Estop=L; fp = 15

s

32 L

32 L

(3.3)

Assuming a decent passband ripple of 0:01 dB, a filter of order 6 600 000

is required. If the passband ripple is reduced to 0:001 dB, the filter order

increases only slightly to 7:5 106 . A filter of order 8:2 106 results, if the

stopband error is reduced to ,130 dB. If the interpolation factor is increased

to lower the influence of the hold operation the filter order increases rapidly.

Estop L

[dB]

,110

,110

,130

,130

,130

216

216

216

218

220

p

s

[dB]

[dB]

0:01

0:001

0:001

0:001

0:001

,158

,158

,178

,184

,190

N

Q

6:6 106

7:5 106

8:2 106

33:9 106

138:9 106

102

115

126

129

132

Table 3.2: Estimated filter order

Recall that to compute one sink sample only a subset of Q coefficients

of the impulse response of the filter is taken (Q = N=L, Sec. 2.5.1). The

computational cost (which is proportional to Q) is consequently about the same

independent of the interpolation factor (last three rows of Table 3.2). However,

the number of filter coefficients that must be stored increases proportionally

to the interpolation factor. For L = 220 over 108 filter coefficients must be

stored. Additionally, direct synthesis of a lowpass filter of order 108 is clearly

beyond practical feasibility.

3.2.2

FIR Filter and Lagrange Interpolation

3.2.2.1

Principle

In Section 2.6 we used the hold operation to convert the highly interpolated

source signal to a continuous-time signal, which was then resampled at the sink

sample rate. Instead of holding the value between two consecutive samples

of the interpolated signal, we now use first order Lagrange interpolation (from

now on simply called linear interpolation) between the two samples to calculate

the sink value (Fig. 3.4).

The frequency response of a linear interpolator has a SINC 2 characteristic.

The noise suppression around the zero crossings of a SINC 2 is much higher

compared to the SINC function of the hold operation. Therefore a substantially smaller interpolation factor is sufficient. The error energy around the

zero crossings for a given interpolation factor L1 = 2k is shown in Table 3.3

and derived in Appendix C. If the error caused by the linear interpolation

(Table 3.3) is compared to the error caused by the hold operation (Table 2.1) it

can be seen that L1 = 27 corresponds to L = 216 and L1 = 29 corresponds to

Discrete

Time

Linear

L1

FIR

Lagrange1.epsiInterFilter

91 21 mm polation

Continuous

Time

Resample

f sink

f source

Figure 3.4: FIR filter followed by linear interpolation

L = 220 .

The interpolation factor can therefore be reduced drastically, if the

hold operation is replaced by linear interpolation.

Sine @ 1 kHz

Sine @ 10 kHz

Sine @ 20 kHz

White Noise

Pink Noise

Error in [dB] for L1 =

2k

27

28

,63:9 , k 12:04 ,148:2 ,160:2

,23:9 , k 12:04 ,108:2 ,120:2

,11:9 , k 12:04 ,96:2 ,108:2

,18:7 , k 12:04 ,103:0 ,115:0

,25:7 , k 12:04 ,110:0 ,122:0

Table 3.3: Error caused by linear interpolation (fsource

29

,172:3

,132:3

,120:3

,127:1

,134:1

=

48 kHz)

So far in this section we assumed that the linear interpolation is calculated

with an infinite resolution on the time axis. Therefore we got a continuous-time

signal after the interpolator (Fig. 3.4).

Linear

Interpolation

L2

Lagrange2.epsi

97 46 mm

L1

f source

FIR

Filter

Interpolation/

Decimation

Filter

Discrete

Time

Hold

Continuous

Time

Resample

f sink

Figure 3.5: FIR filter followed by discrete-time linear interpolation

In a practical realization we only have a finite time resolution of tunit .

tunit = L f1

source

with L = L1 L2 ,

where L2 is the number of resolved samples by the linear interpolator between

two FIR-interpolated samples. The block diagram of Figure 3.4 is therefore

completed with additional function blocks resulting in Figure 3.5.

We actually have a cascade of three filters (Fig. 3.6): the FIR filter HFIR ,

the linear interpolator HLin with the first zero crossing at L1 fsource , and

the hold operation HHold with the zero at L1 L2 fsource . If the following

section we discuss the error contributions of the three filters.

H FIR

H Hold

H Lin

FilterCascade.epsi

108 26 mm

L 1⋅ L 2⋅ f source

L 1⋅ f source

Figure 3.6: Transfer characteristic of FIR filter, linear interpolator, and hold

operation

Figure 3.7 shows the time domain representation of Figure 3.6. The source

samples are interpolated by the FIR filter resulting in the bold samples with

spacing 1=(L1 fsource ) in Figure 3.7. Linear interpolation leads to L2

intermediate samples with spacing 1=(L1 L2 fsource ) = 1=(L fsource ).

Finally, the hold operation converts the discrete-time signal to a continuoustime representation.

x(t)

y(t)

LinTime.epsi

89 29 mm

T=1/(L1⋅f source)

â

x[n]

T=1/(L⋅f source)

Figure 3.7: FIR filter and linear interpolation followed by hold operation

3.2.2.2

Performance Estimation

The error introduced through the three cascaded filters consists of three components. In the first place the stopband attenuation of the FIR filter is weighted

by the SINC 2 transfer function of the linear interpolator, secondly the remaining components of the higher order FIR passband attenuated by the SINC 2 as

well, and thirdly the residuals of the hold operation.

The sum of the weighted stopband attenuation is (using Eq. A.3)

Estop1 2f (s1) 2

source

Z

1

f

)

sin( L1 fsource

f

L fsource

0

!4

df = 23 L1 (s1)2

(3.4)

1

If we assume a white noise signal, we get for the contributions around

the zero crossings of the linear interpolator (Eq. C.7) and the zero-order hold

(Eq. B.7)

4

2

Estop2 7200 (L )4 + 72 (L L )2

1

1

2

(3.5)

The total error for a FIR filter with a finite stopband attenuation s1 is

therefore for the three different audio signals

4

4

2

f

fsig

sig

2

L1 (s1) + 45 L f

+

3 L1 L2 fsource

1

source

4

2

2

2

EWhite 3 L1 (s1) + 7200 (L )4 +

72 (L1 L2 )2

1

ESine 23

EPink 23

L1 (s1)2 + L f

1

source

10 960

4 +

10 472

L1 L2 fsource

2

(3.6)

(3.7)

2

(3.8)

Table 3.4 gives the contribution of the three summands for a white noise

signal (Eq. 3.7) at fsource = 48 kHz and sample values of L1 , L2 , and s1 .

Note that the second summand is reduced by 7 dB and the third by 4.6 dB, if

pink noise is used instead of white noise.

L1 L2

s1

L

[dB]

27

28

29

29

28

27

28

29

210

211

,137

,137

,137

,137

,152

216

216

216

218

220

Weighted

Linear

Zero , order

stopband interpolation

hold

Eq: 3:4

Table 3:3

Table 2:1

[dB]

[dB]

[dB]

,118

,103

,105

,115

,115

,105

,112

,127

,105

,115

,127

,115

,127

,117

,129

Table 3.4: Error contributions from interpolation and finite stopband attenuation (white noise signal)

For the first three rows of Table 3.4 the same interpolation factor L =

L 1 L2 = 216 is used, but the order of the interpolation filter increases and

likewise the number of coefficients that have to be stored.

For a sine wave test signal the second and the third error summand of

Eq. 3.6 depend on the audio signal frequency. Figure 3.8 shows plots using the

parameters in last four rows of Table 3.4. All three summands of Equation 3.6

are plotted with dashed lines and their sum with a solid line.

For the parameters of two plots in the upper half of Figure 3.8 18-bit

performance for full-scale signals is only reached up to about 5 kHz due to the

hold operation (L = 16). The lower two plots represent parameters for 18and 20-bit performance over the full range of input signals.

So far we only discussed the integral over the error contributions. If we

apply a sine wave test signal, the energy will not be equally distributed and

we will get distinct error components in the decimated sink signal. In the

following the size of these ‘peaks’ is calculated.

For a sine wave close to fsource =2 the largest contribution to the stopband

error is caused by the insufficient attenuation of the linear interpolator and the

zero-order hold at the first zero crossing (Fig. 3.6).

The minimal attenuation of the linear interpolator at the first zero crossing

L1 = 256, L2 = 256, δ s1 = −137 dB

L1 = 512, L2 = 128, δ s1 = −137 dB

−100

[dB]

[dB]

−100

−110

−120

−130

−120

100

1000

[Hz]

L1 = 256, L2 =1024, δ s1

−130

10000

1000

10000

100

1000

[Hz]

10000

−100

[dB]

[dB]

100

ErrorSine.eps

[Hz]

108

76

mm

= −137 dB

L1 = 512, L2 =2048, δ s1 = −152 dB

−100

−110

−120

−130

−110

−110

−120

100

1000

[Hz]

−130

10000

Figure 3.8: Error contributions vs signal frequency for sinusoidal audio signals

for f

=

L1 fsource fsource =2 is (Eq. C.2)

fsource

L f2

1

source

!4

=

1

16 (L1)4

(3.9)

and for the zero-order hold we get (Eq. B.2)

fsource

L L 2 f

1

2

source

!2

=

1

4 (L1 L2 )2

(3.10)

For L1 = L2 = 256 the two above equations result in ,108 dB and ,102 dB

respectively. This means that for a source signal close to fsource =2 the sink

signal contains two distinct error components at ,102 dB caused by the hold

operation and two error components at ,108 dB caused by the linear interpolation. The alias frequency of these error components depends on the exact

source and sink sample rates and the signal frequency. Therefore not only the

accumulated stopband error is a matter of concern, but also its distribution.

3.2.2.3

Implementation

Figure 3.9 shows a simplified block diagram of the principle outlined in the

previous section. The two interpolators (by L1 and L2 ) are merged into one

and the FIR filter and the linear interpolator are combined in one block.

Continuous

Time

Discrete

Time

Linear

FIR

& Inter- Lagrange3.epsi

Filter

polation 97 22 mm

L

Hold

Resample

f sink

f source

Figure 3.9: FIR filter with linear interpolator

In the time domain the multiplications of the source signal by the filter transfer functions can be expressed as successive convolutions. We will

discuss further the two implementations that are indicated with brackets in

Equation 3.11.

x ? hFIR ) ? hLin = x ? (hFIR ? hLin )

(

(3.11)

In the left hand case the source signal is interpolated by the FIR filter. Additional intermediate values are calculated by linear interpolation of the oversampled signal. In the right hand case the coefficients of the FIR filter are

linearly interpolated and the resulting filter is then applied to the source signal. Both cases result in the same transfer function, since the convolution is

associative.

The above paragraph describes only the conceptual model. As in the case

of the single stage FIR filter not all values of the interpolated source signal

must be calculated since the interpolation is followed by the decimation. In

the left hand case of Equation 3.11 two successive output samples of the FIR

filter are computed per sink sample. The sink sample is then calculated by

linear interpolation between the two. In the right hand case only one output

sample of the FIR filter is calculated, but each filter coefficient requires an

interpolation.

This second implementation resembles the single stage FIR case. But since

the linear interpolation is performed in real-time less filter coefficients have to

be stored. Instead of the transfer characteristic of a true single stage filter in

Figure 3.1, we get the one in Figure 3.10.

FilterLin.epsi

109 26 mm

δ s1

L 1⋅ L 2⋅ f source

L 1⋅ f source

Figure 3.10: FIR with interpolated impulse response

In Section 3.2.1 (Table 3.2) we estimated the order of a single stage FIR

interpolation/decimation filter and stated that such a filter can not be directly

synthesized. Table 3.5 gives the order N of the FIR filter and the number of

taps Q that must be calculated for the FIR filter if a linear interpolator is used.

Estop L1

[dB]

,118

,115

,112

,115

,127

27

28

29

28

29

p

s

[dB]

[dB]

0:001

0:001

0:001

0:001

0:001

,137

,137

,137

,137

,152

N

Q

13:3 103

26:6 103

53:1 103

104

104

104

26:6 103

57:3 103

104

112

Table 3.5: Estimated filter order

The values of L1 and Estop are taken from Table 3.4. Note that the number

of taps is the same for the first three cases, but the number of stored coefficients

doubles. The parameters for 20-bit performance increase the number of taps

only from 104 to 112.

3.2.3

Alternatives

3.2.3.1

High-Order Coefficient Interpolation

For a single stage FIR implementation with an interpolation factor L = 220

a filter of order 108 is required. If the coefficients are interpolated using first

order Lagrange interpolation the filter order can be reduced to 57 103 as

discussed in the previous sections. The filter order could be further reduced by

Interpolation

L L1 L2 Estop

s1

[dB]

[dB]

Zero order

1st order

220

220

220

29

20

211

2nd order

3rd order

220

220

26

24

214

216

,127

,127

,127

,127

,187

,152

,144

,138

N

Q

137 225 217 131

57 288 112

6 886 108

1671 104

Table 3.6: Coefficient interpolation and filter order

using higher order Lagrange interpolation. Table 3.6 shows the resulting filter

order. Note that the order Q of the actually computed filter stays about the

same, but the reduced storage requirements are traded for a more complicated

coefficient interpolation.

3.2.3.2

Separate Interpolation and Decimation Filter

[JTG+ 94] presented an implementation of a sample-rate converter which performs interpolation by only L = 64 followed by a proprietary hold operation

called ‘controlled validation’ (Fig. 3.11). Before the decimation the error

introduced by the hold operation is attenuated by a second lowpass filter.

’Controlled

Validation’

64

f source

Filter

Philips.epsi

Hold

105

28 mm

1×,2×,3×

64⋅f source

Filter

128⋅f sink

128

f sink

Figure 3.11: Separate interpolation and decimation filters

This special hold operation repeats each interpolated source sample 1-3

times in such a way that only high-frequency error components are produced,

which can be attenuated by the decimation filter. If source and sink sample

rate are the same, each interpolated sample is repeated twice on average. Since

the interpolation filter runs with fsource and the decimation filter runs with

fsink the sink samples are automatically band-limited to half the minimum of

source and sink sample rate by-passing the need to adapt the cutoff frequency

of the filter as in the CONTINUOUS MODE.

3.3

Required Resources

Before we discuss the synthesis problem for high-order digital filters we recapitulate the required resources for the approaches presented in the previous

section. We use the parameters L = 216 and L1 = 28, which results in 18-bit

performance for full-scale signals up to 5kHz and assume a (stereo) audio

signal.

Single Stage FIR Filter

If we assume a filter order of N = 7:5 106 , an interpolation factor of L = 216 ,

and use the hold operation, the number of multiplications for each stereo sink

sample is 2 Q = 2 N=L = 230. For a sink sample rate of 48 kHz we get a

cycle time of 90 ns for the multiplication (and accumulation). This approach

has the drawback that all N = 7:5 106 filter coefficients must be stored in a

way that they can be accessed in real-time.

Interpolation of FIR Impulse Response

If we use linear interpolation on the impulse response with L1 = 28, L2 = 28

(L = 216 ), and a filter order of N = 26 103 the number of multiplications for

the filter is 2 Q = 2 N=L1 = 208. We need one additional multiplication

for each interpolation of the filter coefficients. This results in 3 N=L1 = 312

multiplications and L1 = 28 coefficients to store.

FIR Filter followed by Interpolation

If we interpolate the samples after the FIR filter, two FIR calculations are

needed for each (stereo) channel. One additional multiplication per channel

is used for the linear interpolation. Therefore the number of multiplications is

2 2 Q + 2 = 4 N=L1 + 2 = 418. The number of stored coefficients is the

same as in the previous case.

Discussion

In Section 3.2 we considered different concepts for the realization of the

interpolation/decimation filter. We have seen that a trade-off between the

computational cost and the number of stored coefficients must be made.

The noise estimations in this chapter have been done for full-scale signals.

However, a full-scale sine wave at 20 kHz is not a realistic audio signal. Therefore we could reduce the requirements for higher frequencies. Additionally,

the noise level scales proportionally to the signal level. As a result we have

less distortion for lower level signals. However, these measures reduce the

required filter order only by a small fraction.

So far in this chapter we have only treated the UPMODE. In the DOWNMODE