ニュー 09 09004 09000

0

00

0

09

00

04

40

1

00

00

00

00

0

Fc

C 12w

M

P

0

0

00

0

00

09

04

40

1

0

0

00

09

0

00

SU 211

B w

19

7

Fc

P

2

c1

M

C

00

1

0

6

F

0

90

0

44

1

0

07

35

6

07

35

7

09

0

00

5

73

6

0

1

0

44

C

M

P

00

0

0

40

4

19

00

0

w

12

Fc

00

00

04

1W

21

FC

09

00

0

SU

B

07

35

7

09

Sample of programs

07

35

4

00

ニュー

09

0

>

w

16 F-5

→ 1

4 0

90

04

09

00

4

FI 70w

LE

F-

F

O -4

N 7

LS

FFI 70W

LE

00

00

0

F

O -4

N 7

LS

04

40

0

Version 1.0

Produced in March 1997

51

F-

F-

0

00

00

02

09

00

0

04

40

1

00

16

1

→

09

4 0

FC

00

90

0

04

C 12

M W

09

P

09

00

09

00

4

00

6

4

00

00

00

04

40

0

Sharp Programmable Controller

NEW

00

0

F

O -4

N 8

LR

4

5

73

00

Fc

SU 211

B w

09

00

09

4

5

73

Fc

M 215

U

L

0

4

09

F

04

40

2

00

00

02

00

09

00

6

1

00

4

04

01

w

12

Fc

00

04

00

1w

21

c

F

09

0

00

19

09

4 0

90

04

→

51

F-

SU

B

Fc

C 12

M w

P

16

00

09

C

M

P

07

35

7

FFI 70w

LE

F

O -4

N 7

LS

04

40

0

Satellite

00

07

35

7

07

35

4

40

0

¤

↓

04

2

40

0

0

00

2

0

44

2

0

5

73

7

0

00

0

Introduction

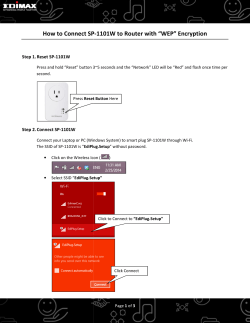

This booklet gave you hits of program plan using various kinds of program example with understood

the great variety and easy to use of application instructions of sharp programmable controller new

satellite JW series.

This booklet is composed of next four chapters and appendix. Please read only necessary passage.

Chapter 1 : Basic circuit

Chapter 2 : Data processing circuit

Chapter 3 : How to use special instruction

Chapter 4 : Example of applications program

Appendix : Description of instruction words

Refer to instruction manual, users manual , and programming manual of each programmable

controller in detail.

Note

・The contents of this manual have been carefully written. However, if you have a problem,

contact your dealer.

・The whole or partial photocopy of this booklet is prohibited.

・Contacts of this booklet may be revised for improvement without notice.

Table of contents

Prior to using this manual

Chapter 1: Basic circuit ••••••••••••••••••••••••••••••••••••••••••

1−1

1−2

1−3

1−4

1−5

1−6

1−7

1−8

1−9

1 −10

1 −11

1 −12

1 −13

1 −14

1 −15

1 −16

1 −17

1 −18

1 −19

1 −20

1 −21

1 −22

1 −23

1 −24

1 −25

1 −26

Normally circuit ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Circuit from which 1 pulse is generated at power ON •••••••••••••••••••••••••••••

Oscillation circuit ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Rise edge differentiation ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Fall edge differentiation •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Self-hold circuit ( reset in priority ) •••••••••••••••••••••••••••••••••••••••••••••••••••••

Self-hold circuit ( set in priority ) •••••••••••••••••••••••••••••••••••••••••••••••••••••••

Priority circuit ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Alternate circuit •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

n bit shift register •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

ON delay timer ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

OFF delay timer •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

ON/OFF delay timer ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

One shot timer at the input rise edge(1) •••••••••••••••••••••••••••••••••••••••••••••

One shot timer at the input rise edge(2) •••••••••••••••••••••••••••••••••••••••••••••

One shot timer at the input fall edge ••••••••••••••••••••••••••••••••••••••••••••••••••

One shot timer at rise/fall edge ••••••••••••••••••••••••••••••••••••••••••••••••••••••••

ON delay one shot timer ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Equivalent pulse generation circuit ••••••••••••••••••••••••••••••••••••••••••••••••••••

Duty variable pulse generator circuit(1) ••••••••••••••••••••••••••••••••••••••••••••••

Duty variable pulse generator circuit(2) ••••••••••••••••••••••••••••••••••••••••••••••

Long time timer(1) ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Long time timer(2) ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Large capacity counter(1) •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Large capacity counter(2) •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Counter that counts at the rise or fall edge of counter input •••••••••••••••••••••

Chapter 2 : Data processing circuit •••••••••••••••••••••••••••••

2−1

2−2

2−3

2−4

2−5

2−6

2−7

2−8

2−9

1•1 to 1•18

1• 1

1• 2

1• 3

1• 4

1• 4

1• 5

1• 6

1• 7

1• 8

1• 9

1•10

1•10

1•11

1•11

1•12

1•12

1•13

1•13

1•14

1•15

1•15

1•16

1•16

1•17

1•17

1•18

2•1 to 2•74

Change of operation execution condition •••••••••••••••••••••••••••••••••••••••••••••

Register clear ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Masking data •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Set/reset bits •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Decomposition of number •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Composition of number ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Comparison with setting value ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Window comparator •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Comparator having undetectable zone •••••••••••••••••••••••••••••••••••••••••••••••

2• 1

2• 2

2• 2

2• 3

2• 4

2• 5

2• 6

2• 8

2• 9

2 −10

2 −11

2 −12

2 −13

2 −14

2 −15

2 −16

2 −17

2 −18

2 −19

2 −20

2 −21

2 −22

2 −23

2 −24

2 −25

2 −26

2 −27

2 −28

2 −29

2 −30

2 −31

2 −32

2 −33

2 −34

2 −35

2 −36

2 −37

2 −38

2 −39

2 −40

2 −41

2 −42

2 −43

2 −44

Timer that multiple number of set points ••••••••••••••••••••••••••••••••••••••••••••• 2•10

Obtaining the BCD result by the signed absolute value ••••••••••••••••••••••••••• 2•11

Multiplication of BCD 8 digits ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•12

BCD 8 digits ÷ BCD 4 digits ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•14

Division of BCD 4 digits ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•15

Drum seqencer •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•19

Timer current value external output ••••••••••••••••••••••••••••••••••••••••••••••••••• 2•20

Counter current value external output •••••••••••••••••••••••••••••••••••••••••••••••• 2•23

Input of timer setting value from external device ••••••••••••••••••••••••••••••••••• 2•25

Input of counter setting value from external device •••••••••••••••••••••••••••••••• 2•27

Input of multiple numbers of timer and counter setting value from external devices •••••••••••••••• 2•30

Hour/minute/second setting subtract timer •••••••••••••••••••••••••••••••••••••••••• 2•34

Dynamic input ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•35

Dynamic output ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•37

Synchronous type FIFO stack register ••••••••••••••••••••••••••••••••••••••••••••••• 2•39

Data distribution •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•40

Data extraction •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•43

Insert data •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•46

Delete data •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•48

Data search(1) •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•50

Data search(2) •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•51

Data verification ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•53

Obtaining the minimum and maximum value of BCD 4 digits •••••••••••••••••••• 2•55

Obtaining mean value of BCD 2 digits numbers •••••••••••••••••••••••••••••••••••• 2•57

Clear area assignment of file register •••••••••••••••••••••••••••••••••••••••••••••••• 2•59

Read of a number from the ten keyboard •••••••••••••••••••••••••••••••••••••••••••• 2•60

8 to 256 decoder •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•62

256 to 8 encoder •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•63

7SEG encoder •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•65

Conversion from gray code to binary code •••••••••••••••••••••••••••••••••••••••••• 2•66

BCD 6 digits up/down counter ••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•67

24 bits shift register •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•69

Measurement of scan time ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•71

BCD code creation ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•72

Display current value of the high-speed counter with sign ••••••••••••••••••••••• 2•73

Chapter 3 : How to use special instructions ••••••••••••••••••

3−1

3−2

3−3

3−4

3•1 to 3•22

I/O refresh instruction and interruption processing •••••••••••••••••••••••••••••••••

Special I/O data refresh instruction (F-81) ••••••••••••••••••••••••••••••••••••••••••••

Reading from special I/O (F-85) and writing to special I/O (F-86) •••••••••••••••

Send instruction (F-204) and receive instruction (F-205) ••••••••••••••••••••••••••

3• 1

3• 5

3• 8

3•12

3 − 5 MD (maintenance display) instruction (F-20) •••••••••••••••••••••••••••••••••••••••• 3•17

Chapter 4 : Example of application programs ••••••••••••••••

4•1 to 4•31

4 − 1 Detection of position deviation ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

4 − 2 Obtain folding length an iron plate (using F-23 (COS) instruction) ••••••••••••••

4 − 3 Search and delete PC board cartridges •••••••••••••••••••••••••••••••••••••••••••••••

4 − 4 Warehouse/delivery management of automatic warehouse •••••••••••••••••••••••

4 − 5 Analog output voltage setting •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

4 − 6 Data verification •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

4 − 7 Slit data creation •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

4 − 8 Scale conversion ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

4 − 9 Day or night judgment ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

4 −10 Switchover of operation time ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

4 −11 Communication between PCs using computer link •••••••••••••••••••••••••••••••••

4• 1

4• 2

4• 3

4• 5

4• 8

4•10

4•14

4•17

4•24

4•26

4•29

Appendix : Description of instruction words •••••••••••••••••••••••• App•1 to App•11

Prior to using this model

1.

Applicable models

・Programs described in this manual can be used with the following JW series PCs.

PC model name

Module(CPU) model name

JW10

JW-1324K, JW-1424K, JW-1624K

JW20H

JW-21CU, JW-22CU

JW30H

JW-31CUH, JW-32CUH, JW-33CUH

JW50H

JW-50CUH

JW70H

JW-70CUH

JW100H

JW-100CUH

J-board

Z-311J, Z-312J

Note 1: Some programs described in this manual are limited to use with specific PC models.

Programs having no noted applicable PC models can be used with all the models above.

Note 2: J-board has the same instruction word system as that of JW20H. Programs nominated to

be applicable with JW20H are also applicable with J-board.

Note 3: Some programs in this manual can be used with the previous models (W10/W16/W51/

W100/W70H/W100H).

2.

Numeric value expression methods

1 ) The following notations are used for numeric value expression method of addresses and set values:

Octal notation : Put (8) after the numeric value. Ex.: 377(8)

Decimal notation : Decimal notation: Put (D) after the numeric value or no mark. Ex: 255(D), 255

Hexadecimal notation : Put (H) after the numeric value. Ex.: FF(H)

2 ) The following methods are employed for expressing the register data length:

Byte (8 bit) processing

: Indicates register number only.

Ex.: 09000

Word (16 bit) processing

: Affix “w” to register number.

Ex.: 09000w (Use 09000, 09001)

Double words (32 bit) processing : Affix “d” to register number.

Ex.: 09000d (Use 09000 to 09003)

3.

Programs

1 ) The program examples shown in this manual are created based on the minimum requirements for

operation. Therefore, at actual programming, you may need to add a conditional signal to make a

command signal effective/ineffective or add an interlock signal.

2 ) To express data memory numbers such as relay numbers, numbers are applied in this manual as

they are with JW10. This is because JW10 has fixed input and output relay areas (input: from 00000,

output: from 00400), and data memory area such as JW10 registers are contained in other PC’s data

memory area. However, in the case of PCs having maximum control input/output of 256 (JW-21CU,

J-board), these PCs have input/output relay area from 00000 to 00377, and output relay numbers

nominated in this manual should be replaced with relay numbers available for each PC. Relay num

bers in the program examples of this manual are freely allocated. You have to input the required

numbers of relays to match with your system.

3 ) This manual doesn’t use double word instruction (such as F-00d or F-10d) for application instruc

tions. This is because JW10 does not have double word instruction function. In some models such

as JW30H, use of double word instruction may simplify program.

Ex.: Transfer data from register 09000 to 09003 to register 19000 to 19003

a ) Program in this manual b ) Program available to be created by JW30H

F-00w

09000 19000

XFER

F-00d

09000 19000

XFER

F-00w

09002 19002

XFER

or

F-70

FILE

004

09000 19000

4 ) This manual uses only F-70 (“n” bytes batch transfer) and F-70w ((“n” word batch transfer) which

can use indirect address. This is because JW10 and JW20H have no other instructions which can

use indirect address. By using indirect address for JW30H or the like, some programs may be simpli

fied.

Ex. 1: Transfer contents in register numbers 09000, 09001 and 09002 as indirect address to the 19000.

a ) Program in this manual b ) Program available to be created by JW30H

F-70

FILE

001 @09000 19000

F-00

@09000 19000

XFER

Ex. 2: Set an indirect address register 19000 to the registers 09000 to 09002.

a ) Program in this manual b ) Program available to be created by JW30H

F-08w

005000 09000

OCT

F-01

BCD

00

F-100

19000 09000

ADRS

09002

5 ) END instruction (F-40) is omitted.

Chapter 1: Basic circuit

This chapter introduces basic circuits using contacts, coils, timers, and counter instructions which are

basic instructions of ladder program.

1−1

1−2

1−3

1−4

1−5

1−6

1−7

1−8

1−9

1 −10

1 −11

1 −12

1 −13

1 −14

1 −15

1 −16

1 −17

1 −18

1 −19

1 −20

1 −21

1 −22

1 −23

1 −24

1 −25

1 −26

Normally ON circuit ••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Circuit from which 1 pulse is generated at power ON ••••••••••••••

Oscillation circuit •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Rise edge differentiation ••••••••••••••••••••••••••••••••••••••••••••••••••

Fall edge differentiation •••••••••••••••••••••••••••••••••••••••••••••••••••

Self-hold circuit (reset in priority) ••••••••••••••••••••••••••••••••••••••••

Self-hold circuit (set in priority) ••••••••••••••••••••••••••••••••••••••••••

Priority circuit •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Alternate circuit •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

n bit shift register •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

ON delay timer •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

OFF delay timer ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

ON/OFF delay timer •••••••••••••••••••••••••••••••••••••••••••••••••••••••

One shot timer at the input rise edge(1) •••••••••••••••••••••••••••••••

One shot timer at the input rise edge(2) •••••••••••••••••••••••••••••••

One shot timer at the input fall edge •••••••••••••••••••••••••••••••••••

One shot timer at rise/fall edge ••••••••••••••••••••••••••••••••••••••••••

ON delay one shot timer ••••••••••••••••••••••••••••••••••••••••••••••••••

Equivalent pulse generation circuit •••••••••••••••••••••••••••••••••••••

Duty variable pulse generator circuit(1) •••••••••••••••••••••••••••••••

Duty variable pulse generator circuit(2) •••••••••••••••••••••••••••••••

Long time timer(1) •••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Long time timer(2) •••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Large capacity counter(1) ••••••••••••••••••••••••••••••••••••••••••••••••

Large capacity counter(2) ••••••••••••••••••••••••••••••••••••••••••••••••

Counter that counts at the rise or fall edge of counter input •••••••

1• 1

1• 2

1• 3

1• 4

1• 4

1• 5

1• 6

1• 7

1• 8

1• 9

1•10

1•10

1•11

1•11

1•12

1•12

1•13

1•13

1•14

1•15

1•15

1•16

1•16

1•17

1•17

1•18

1 - 1 Normally ON circuit

00400

07366

STR

NOT

OUT

● As

special relay 07366 is normally an OFF contact, coil

00400 is normally ON. If 00400 is set in “area to be OFF

at stoppage,” this coil is turned OFF at switching program mode or when the PC stops operation by self-diagnosis function. Therefore this special relay can be used

as indication of PC run condition.

use “b” contact of 07366 for input condition of application instruction.

(Ex.1) In case of an instruction to be executed when

input signal is ON.

Note 1 To set an output to “area to be OFF at stoppage,”

model.

PC model name

System memory

JW10

#206

JW20H

#232, #233

JW30H

#232, #233, #252, #253

JW50H/70H/100H

#232, #233

00400

Reference In order to execute operation of the application instruction operation in every operation cycle,

07366

use the following system memory. For details, see

programming manual or user’s manual of each

07366

Normally executes

F-12

Compare contents between

09000 09001

CMP

09000 with 09001

(Ex.2) In case of an instruction to be executed when

input signal is changed OFF to ON.

F-47

ONLS Set level operation condition

07366

Normally executes

F-00

XFER

09000 09001

Transfer contents

of 09000 to 09001

F-48

ONLR Reset level operation condition

1-1

1 - 2 Circuit from which 1 pulse is generated at power ON

04001

04000

07366

04001

STR

NOT

04001

OUT

STR

04000

NOT

07366

OUT

Power ON

I/O

1 scan time

User program execution

I/O

User program execution

I/O

04001

Note 2 No pulse is generated when 04001 is in the latch

function assigned area.

(Reason) 04001 turns ON upon preceding power

04000

ON and retains ON during a power failure time.

To assign the latch function area, set the following

04001

Note 1 No pulse is generated when the program sequence

is changed.

07366

04001

system memory. For details, see appropriate programming manual or user’s manual for that model

PC.

System memory

PC model

#230, 231

JW10

04000

04001

Power ON

I/O

User program execution

I/O

User program execution

04001

OUT 04001

04000

JW20H

#230, #231

JW30H

#230, #231, #250, #251

JW50H/70H/100H

#230, #231

Note 3 This pulse is used to clear registers at power ON

and to preset constants.

Ex.: Clear register 09000 contents at power ON.

ÅEIn case of JW50H/70H/100H

04000

STR NOT 04001(04001 is already ON)

F-01

BCD

00

09000

・In case of JW10, JW20H, and JW30H

F-47 Set level operation

ONLS condition

04000

F-01

BCD

00

09000

F-48 Reset level operation

ONLR condition

In case of the JW10, JW20H, or JW30H, when this

pulse is used as input signal for instructions which

are triggered by rising edge of an input signal (such

as F-01), it should be used within the level operation conditions.

Reference An initializing pulse (07362) is provided as a

special relay to turn ON for one scan time interval

at turning ON the power.

1-2

1 - 3 Oscillation circuit

04000

04000

STR

NOT

04000

OUT

● ON

and OFF are repeated at every 1 scan.

04000

Reference Method to perform operation at every 1 scan cycle

When the oscillator circuit clock is programmed for

1scan time

the data processing instruction execution condition,

operation takes place every 1 scan cycle.

I/O User program execution I/O User program execution I/O

1scan time

04000

04000

04000

Depends on the location where this instruction is written.

This pulse is used for the basic clock of the blink circuit

04000

or operation start signal at every 1 scan.

Note 1 At which point of the scan cycle it changes from

ON to OFF depends on where the instruction is

04000

F-00

XFER

∼

∼

∼

∼

∼

∼

∼

∼

04000

F-00

XFER

09001

F-13

AND

c

09100

n+1

n+2

In case operation has to be done at every operational cycle, the following programming is required.

04000

04000

09101

∼

∼

00010

n

09000

09100

04000

04000

b

∼

∼

09000

09000

04000

written in program steps.

a

F-63

INC

04000

F-63

INC

09000

F-63

INC

09000

09101

04000

I/O User program execution① I/O User program execution② I/O

04000

04000

09000

00010

c Executed

b Executed

a Not executed

c Not executed

(until 00010 changes from

OFF to ON next time)

b Not executed

a Executed

n n+1 n+2 n+3 n+4

Using F-47 (setting level operation condition) or F48 (reset level operation condition), you can execute

cycle operation of each operation.

When the operation “c” is executed in the scan cycle

of the user program execution (1), the result of

“a”executed in scan cycle 1 step before is used for

the operation of “c” because “a” is not executed in

this scan cycle.

F-47

ONLS

07366

F-63

INC

09000

Normally OFF contact

F-48

ONLR

See “2-1 Change of operation execution condition”.

1-3

1 - 4 Rise edge differentiation

00000

04000

04001

04001

00000

STR

00000

AND

04001

OUT

04000

STR

NOT

OUT

●

When 00000 changes from OFF to ON, 04000 goes ON

for a period of 1 scan time.

I/O

User program execution

I/O

User program execution

I/O

00000

04001

Note 1 No pulse is generated when the program sequence

is changed.

Reference

Use of F-44 completes the operation by 1 instruction.

00000

(Data memory)

00000

1 scan time

F-44

04000

↑

04000

04001

1 - 5 Fall edge differentiation

00000

04001

00000

●

STR

04000

04001

When 00000 changes from OFF to ON, 04000 goes ON

for a period of 1 scan time.

I/O

User program execution

I/O

User program execution

04000

04001

1-4

00000

AND

04001

OUT

04000

STR

00000

OUT

04001

Note 1 No pulse is generated when the program sequence

is changed.

Reference

Use of F-44 completes the operation by 1 instruction.

00000

(Data memory)

I/O

NOT

1 scan time

00000

F-45

↓

04000

1 - 6 Self-hold circuit (reset in priority)

00000

00010

(Set)

(Reset)

04000

04000

STR

00000

OR

04000

AND

NOT

00010

OUT

●

04000

When the set input is turned ON once with the reset

Note 1 When the data memory in the latch function as-

input in ON state (continuing in the ladder chart), the

state is retained even after the set input went OFF, until

signed area is used for an output, the state immediately before a power failure can be retained, pro-

the reset input is turned ON or power is turned OFF.

vided that the normally open contact is used for the

external contact and AND is used by program, the

I/O User program execution I/O User program execution I/O User program execution

Set input

00000

(Data memor)

Reset input

00010

self-fold will be reset when the input power supply

is shut off before the power supply of the PC.

Reference The self latch circuit also can be constructed

using F-32 (set coil) or F-33 (reset coil) instructions.

(Data memory)

04000

00000

F-32

SET

04000

F-33

RST

04000

(Set)

00010

(Reset)

1-5

1 - 7 Self-hold circuit (with set in priority)

04000

00000

(Set)

04000

00010

(Reset)

STR

00000

STR

04000

AND

NOT

OR

STR

00010

OUT

●

When the set input is turned ON once regardless of ON

and OFF state of the reset input, the output is turned ON

and the state is retained even after the set input gone

Note When the data memory in the latch function assigned area is used for an output , the state immediately before a power failure can be retained , provided that the normally open contact is used for the

OFF.

● Even if the reset input is turned OFF (non-continuing in

the ladder chart) with the set input in the OFF state, the

output retains the ON state with reset being invalid.

●

Output will be turned OFF when the reset is turned ON

or power is turned OFF with the set input in the OFF

state.

Set input

00000

04000

external contact of the reset input and made AND

NOT program-wise.

●

If the normally closed contact is used for the external

contact and AND is used by program ;

1If the input power supply module shut OFF before the

PC power supply when a power failure is encountered

while the set input is OFF , reset will be carried out even

if the reset external contact is closed.

00010

2If the input power supply should rise later than the PC

power supply when a power failure is restored while the

04000

set input is OFF , reset will be carried out even if the

reset external contact is closed.

Reset input

Reference The self latch circuit also can be constructed

using F-32 (set coil) or F-33 (reset coil) instructions.

00010

(Reset)

00000

(Set)

1-6

F-33

RST

04000

F-32

SET

04000

1 - 8 Priority circuit

(a) In case input is a level signal

STR

00000

(Input A)

00001

04001

04000

04000

04001

AND

NOT

04000

STR

00001

NOT

OUT

●

Input A or input B whichever comes first takes preference over the other and the input that follows will be

treated invalid.

04001

OUT

AND

(Input B)

00000

04000

04001

Note 1 If the input A and input B go on in the same scan

cycle , the one appearing first in the program takes

preference over the other.

Input A

00000

04000

Input B

00001

04001

Input B comes first

Input A comes first

(b) In case input is a pulse signal

00000

04001

(Input A)

04000

00001

(Input B)

04001

00002

04000

(Reset)

04000

00002

04001

(Reset)

STR

00000

OR

04000

AND

NOT

04001

AND

NOT

00002

OUT

04000

STR

00001

OR

04001

AND

NOT

04000

AND

NOT

00002

OUT

●

04001

This signal is used for the output that should not turn ON

at the same time (forward/reverse rotation of the motor

and so on).

1-7

1 - 9 Alternate circuit

STR

00000

F-44

04000

F-44

↑

(Input)

04000

00400

00400

(Output)

04000

00000

00400

OUT

04000

STR

04000

AND

NOT

00400

STR

NOT

04000

AND

00400

OR

STR

OUT

●

Each time the input goes ON, it makes the output inverted. It is possible to produce an alternate output when

connected with the contact of the momentary switch.

●

When this circuit is used repeatedly for n-times, it will

00400

(Input)

00000 04000 (Output)

00400 constitute the divider circuit of n-stages.

00000

F-44

04000

↑

04000

00400

04000

00400

①

00400

②

③

④

⑤

⑥

⑦

⑧

00000

00400

00401

00400

F-45

04001

↓

04001

00401

04001

00401

00401

F-45

00401

00402

00403

04002

↓

04002

00402

04002

00402

00402

F-45

00402

(Note) F-45 (fall edge differentiation) after the second stage.

04003

↓

04003

00403

(Reference) When output of 00400 to 00403 is used, it constitute the binary

counter.

00403

00000

04003

1-8

00403

Same as

F-63

INC

コ0040

1 - 10 n bit shift register

00000

04000

F-44

↑

STR

Rise edge differntiation

(Shift input)

04000

04103

04000

04104

04000

04102

00002

04104

(Reset input)

00002

F-44

OUT

04000

STR

04000

AND

04103

STR

04103

00000

NOT

04000

AND

04000

04103

04000

04101

04000

04102

04000

04100

04000

04101

04000

00001

00002

04102

00002

04101

00002

04100

OR

STR

AND

NOT

00002

OUT

04104

00000 Shift input

(Data input)

04000

04104

04100

00001 Data input

00002 Reset input

Shift input 00000

Data input 00001

Reset input 00002

Shift input 00000

04100

04101

04102

04103

04104

Note 1 To retain the shift state at a time of power failure, it

becomes necessary to use the latch function assigned data memory area for 04100 to 04104.

Reference Use of F-60 enables to constitute the shift register by one instruction.

Differentiation

signal 04000

Data input 00001

07366

(Shift direction)

00001

Reset input 00002

(Data input)

04104

00000

F-60

SFR

コ0410

(Shift input)

04103

00002

04102

(Reset input)

04101

04100

1-9

1 - 11 ON delay timer

00000

TMR

000

0100

STR

00000

TMR

000

0100

00400

TMR000

STR

TMR

000

OUT

Note 2 If a power failure is met while the input is ON, the

state of the output upon power recovery differs de-

00000

TMR000

●

Setting time

(10 second)

Setting time

(10 second)

Output turns ON with a delay by the setting time after

the input turns ON. If the input ON time is less than the

setting time, the output would not turn ON.

●

00400

When the input turned OFF, it also makes the output

turned OFF.

Note 1 By means of the system memory #201, it would be

possible to make choice whether the current value

pending on how #201 is programmed.

(a) #201 is 000(8) - Current value is reset

After power recovery, the output turns ON with a

delay by the setting time.

(b) #201 is 001(8) - Current value is retained

(b)-1 If time is up before the power failure :

After power recovery, the output turns ON in

the first scan cycle.

(b)-2

is reset or retained at a time of power failure.

{

Setting #201

If time is not up before the power failure :

After power recovery, the output turns ON with

a delay by the time of (setting value - current

value at the time of power failure).

000(8) The current value is reset

(the setting value is assumed).

001(8) The current value is retained.

1 - 12 OFF delay timer

00000

TMR

000

STR

0100

NOT

00000

TMR

000

0100

00400

TMR000

STR

NOT

TMR

OUT

after the input turns OFF. If the input OFF time is

less than the setting time, the output would not turn

TMR000

●

●

Setting time

(10 second)

Setting time

(10 second)

Output turns OFF with a delay by the setting time after

the input turns OFF. If the input OFF time is less than

OFF.

(a) #201 is 000(8) - Current value is reset

After power recovery, the output turns ON for a

period of the setting time.

(b) #201 is 001(8) - Current value is retained

(b)-1 If time is up before the power failure :

the setting time, the output would not turn OFF.

When the input turned OFF, it also makes the output

turned OFF.

00400

Note1Output turns OFF with a delay by the setting time

00000

00400

000

The output would not turn ON after power recovery.

(b)-2

If time is not up before the power failure :

After power recovery, the output turns ON for a

period of (setting value - current value at the

time of power failure).

1-10

1 - 13 ON/OFF delay timer

00000

TMR

000

ON delay setup

t1

0100

STR

00000

TMR

000

0100

TMR000

TMR

001

STR

0050

OFF delay setup

t2

NOT

TMR

TMR

001

0050

00400

TMR001

STR

NOT

TMR

OUT

TON

000

001

00400

TOFF

●

00000

The output turns ON with a delay of t1 after the input has

turned ON, and the output turns OFF with a delay of t2

after the input has turned OFF.

TMR000

TMR000

If the input ON time (Ton) is smaller than the ON delay

setting time (t1), the output would not turn ON.

TMR001

Note 1 For state of the output at a time of power failure,

refer to "1-11 ON delay timer" and "1-12 OFF delay

●

Not turn ON

timer".

00400

t1

t2

(10 sec.)

t1

(5 sec.)

(10 sec.)

1 - 14 One shot timer at the input rise edge (1)

STR 00000

TMR

000

0030

ON delay setup

t1

00000

TMR

000

0030

00000

TMR000

TON

STR

00400

NOT

TMR

000

AND 00000

OUT

00400

TON

●

At rising edge of the input signal (OFF to ON) , a pulse

●

whose width is the setting time (t1) is issued.

If the input ON time (Ton) is smaller than the setting

00000

TMR000

time(T1), the width of the output pulse will be Ton.

TMR000

00400

t1

(3 sec.)

t1

(3 sec.)

1-11

1 - 15 One shot timer at the input rise edge (2)

STR

(A)

F-44

↓

00000

00400

TMR000

00000

F-44

OR

00400

AND

04000

04001

TMR

0010

000

ON delay setup

t1

00400

NOT

TMR

000

OUT

00400

TMR

000

0010

TON

TON

●

00000

(A)

●

t1+Δt

00400

t1+Δt

Δt

At rising edge of the input signal (OFF to ON) , a pulse

whose width is the (setting time t1 + Δt) is issued.

Where, Δt is 1 scan time.

Irrespective of the input ON time (Ton) , the output pulse

width of the output will be t1 + Δt.

Δt

TMR000

t1

t1

(1 sec.)

(1 sec.)

1 - 16 One shot timer at the input fall edge

STR

00000

TMR

010

0020

ON delay setup

t1

NOT

00000

TMR

010

0020

TMR010

00400

00000

STR

NOT

AND

NOT

OUT

TMR010

00000

00400

ing on how the system memory #201 is programmed.

t1

(2 sec.)

●

010

Note1 When a power failure is met while the input is OFF,

the output after power recovery may differ depend-

00000

00400

TMR

At falling edge of the input signal (ON to OFF), a pulse

whose width is the setting time issued.

(a) #201 is 000(8) - Current value is reset

After power recovery, the output turns ON for a

period of the setting time.

(b) #201 is 000(8) - Current value is retained

(b)-1

(b)-2

If time is not up before the power failure :

The output would not turn ON after power recovery.

If time is not up before the power failure :

After power recovery, the output turns ON for a

period of (setting value - current value at the

time of power failure ).

1-12

1 - 17 One shot timer at rise/fall edge

00000

TMR

000

0010

STR

00000

TMR

000

ON delay setup

t1

0010

STR NOT

00000

TMR

001

0010

OFF delay setup

t2

TMR

00000

TMR001

00000

00400

001

0010

STR

TMR000

00000

NOT

TMR

AND

00000

STR

NOT

AND

NOT

OR STR

TMR

TMR000

TMR001

001

00000

OUT

00000

000

00400

●

At rising and falling edge of the input, output signals (t1

●

and t2) are turned ON, respectively.

This signal is used to detect a change in the state of the

●

input.

Also used to multiply input pulse frequency.

00400

t1

t2

1 - 18 ON delay one shot timer

STR

(A)

F-44

↓

00000

F-44

04000

TMR001

00000

OR

AND

04000

TMR

000

0010

ON delay setup

t1

04000

NOT

TMR

001

OUT

04000

TMR

000

0010

TMR000

TMR000

TMR

001

TMR001

0020

ON delay setup

t2

STR

TMR

TMR

000

001

0020

00400

STR

AND

OUT

NOT

TMR

000

TMR

001

00400

1-13

TON

●

The output having the pulse width of t2 is issued with a

delay of setting value t1 from the rise edge of the input.

●

Change of the input during the time (t1+ t2) is disregarded.

00000

(A)

04000

TMR000

Δt

TMR001

00400

t1

t2

Δt … 1 scan time

1 - 19 Equivalent pulse generation circuit

STR

AND

00000

TMR000

00400

TMR000

00400

NOT

0030

00000

00400

0030

NOT

TMR000

00400

1-14

t1

000

00400

TMR

AND

NOT

OR

STR

000

00400

AND

00000

OUT

00400

While the input is ON, the pulse whose ON and OFF

periods are equal (50% duty cycle) is issued. ON and

OFF period may be set as desired using the TMR set-

t1 t1

t1

t1+Δt

TMR

AND

●

Δt

000

000

ON delay setup

t1

STR

00000

TMR

TMR

TMR

000

STR

TMR000

00000

ting value (t1). The pulse width shall be t1 + Δt.

Δt … 1 scan time

1 - 20 Duty variable pulse generator circuit (1)

STR

TMR001

00000

TMR

000

0010

ON delay setup

t1

AND

00000

NOT

TMR

001

TMR

TMR000

TMR

001

0020

ON delay setup

t2

000

0010

STR

TMR

000

TMR

001

00400

0020

OUT

●

00000

t1

t2+Δt

TMR000

(00400)

t2

00400

When the input is ON, the pulse having t2+ Δt for the

ON period and t1 for the OFF period is issued.

Δt

TMR001

Δt … 1 scan time

1 - 21 Duty variable pulse generator circuit (2)

STR

TMR001

00000

TMR

000

0010

ON delay setup

t1

AND

TMR

00000

NOT

TMR

001

000

0010

TMR

001

0040

ON delay setup

t2

TMR

001

00400

●

00000

t1

TMR000

t2−t1+Δt

t2

When the input is ON, the pulse having t2 - t1 + Δt for the

ON period and t1 for the OFF period is issued.

Note 1 t1 must be smaller than t2.

Δt

TMR001

Δt … 1 scan time

1-15

1 - 22 Long time timer (1)

00000

TMR

000

0100

ON delay setup

t1

STR

00000

TMR

000

0100

TMR000

TMR

001

0010

ON delay setup

t2

STR

TMR

TMR

001

0010

00400

TMR001

STR

TMR

OUT

●

00000

TMR001

t1

TMR000

000

001

00400

After the input turned ON, the output becomes ON with

a delay of t1 + t2.

t2

t1+t2

1 - 23 Long time timer (2)

STR

TMR000

00000

TMR

000

0050

ON delay setup

t1 AND

00000

NOT

TMR

TMR

000

TMR000

0050

CNT

001

00000

0020

Counter setup

n

STR

STR

TMR

CNT

OUT

TMR000

●

Δt t1

t1

(t1+Δt)

CNT001

t1+(t1+Δt)×(n−1)≒(t1+Δt)×n

Δt … 1 scan time

1-16

001

0020

STR

00000

000

00000

NOT

00400

CNT001

000

CNT

001

00400

After the input turned ON, the output becomes ON with

a delay of (t1 + Δt ) × n.

1 - 24 Large capacity counter (1)

STR

00000

Setting value n1

00001

CNT

004

CNT004

1000

STR

AND

00000

00001

NOT

CNT

CNT

004

004

CNT004

1000

Setting value n2

CNT

005

00001

0050

00400

CNT005

STR

CNT

004

STR

00001

CNT

005

0050

STR

Setting value 1000×50=50000

(CNT is ON reset)

CNT

OUT

Reset input

00001

●

Counter input

00000

005

00400

When the setting value exceeds 1999, programming it

in the above manner will realize the counter of the setting value (n1 × n2).

Δt

CNT004

00400

Δt … 1 scan time

1 - 25 Large capacity counter (2)

00000

Setting value n1

CNT

006

00001

1999

STR

00000

STR

00001

CNT

006

1999

00000

CNT006

STR

Setting value n2

CNT

007

00001

1002

00400

CNT007

AND

00000

CNT

006

STR

00001

CNT

007

1002

STR

Setting value 1999 + 1002−1=3000

(CNT is ON reset)

Reset input

00001

●

n1

007

00400

It establishes the counter of the setting value (n1 +n2 1).

Counter input

00000

CNT006

OUT

CNT

n2

(A)

00400

1-17

1 - 26 Counter that counts at the rise or fall edge of counter input

STR

00000

F-44

F-44

↓

STR

F-44

00000

00000

F-44

CNT

100

1000

OR

↓

00001

00400

CNT100

00000

NOT

STR

STR

00001

CNT

100

1000

STR

CNT

OUT

Reset input

00001

●

Current value

00400

1-18

1000

999

998

997

1

0

0

0

1000

00400

It is the counter that decrements when the counter input

changes from OFF to ON or ON to OFF.

Counter input

00000

100

Chapter 2: Data processing circuit

This chapter mainly introduces general data processing circuit using a variety of application instructions of JW series PCs.

2 − 1 Change of operation execution condition •••••••••••••••••••••••••••••• 2• 1

2 − 2 Register clear •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2• 2

2 − 3 Masking data •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2• 2

2 − 4 Set/reset bits ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2• 3

2 − 5 Decomposition of number ••••••••••••••••••••••••••••••••••••••••••••••••• 2• 4

2 − 6 Composition of number •••••••••••••••••••••••••••••••••••••••••••••••••••• 2• 5

2 − 7 Comparison with setting value ••••••••••••••••••••••••••••••••••••••••••• 2• 6

2 − 8 Window comparator •••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2• 8

2 − 9 Comparator having undetectable zone ••••••••••••••••••••••••••••••••• 2• 9

2 −10 Timer that multiple number of set points •••••••••••••••••••••••••••••• 2•10

2 −11 Obtaining the BCD result by the signed absolute value •••••••••••• 2•11

2 −12 Multiplication of BCD 8 digits •••••••••••••••••••••••••••••••••••••••••••• 2•12

2 −13 BCD 8 digits ÷ BCD 2 digits •••••••••••••••••••••••••••••••••••••••••••• 2•14

2 −14 Division of BCD 4 digits ••••••••••••••••••••••••••••••••••••••••••••••••••• 2•15

2 −15 Drum sequencer ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•19

2 −16 Timer current value external output •••••••••••••••••••••••••••••••••••• 2•20

2 −17 Counter current value external output ••••••••••••••••••••••••••••••••• 2•23

2 −18 Input of timer setting value from external device •••••••••••••••••••• 2•25

2 −19 Input of counter setting value from external device ••••••••••••••••• 2•27

2 −20 Input of multiple numbers of timer and counter setting value from external devices ••••••••••••• 2•30

2 −21 Hour/minute/second setting subtract timer •••••••••••••••••••••••••••• 2•34

2 −22 Dynamic input •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•35

2 −23 Dynamic output ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•37

2 −24 Synchronous type FIFO stack register ••••••••••••••••••••••••••••••••• 2•39

2 −25 Data distribution (storage to data table) ••••••••••••••••••••••••••••••• 2•40

2 −26 Data extraction (take out data from table) ••••••••••••••••••••••••••••• 2•43

2 −27 Insert data ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•46

2 −28 Delete data •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•48

2 −29 Data search(1) •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•50

2 −30 Data search(2) •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•51

2 −31 Data verification •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• 2•53

2 −32 Obtaining the minimum and maximum value of BCD 4 digits ••••• 2•55

2 −33 Obtaining mean value of BCD 2 digits numbers ••••••••••••••••••••• 2•57

2 −34

2 −35

2 −36

2 −37

2 −38

2 −39

2 −40

2 −41

2 −42

2 −43

2 −44

Clear area assignment of file register ••••••••••••••••••••••••••••••••••

Read of a number from the ten keyboard •••••••••••••••••••••••••••••

8 to 256 decoder •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

256 to 8 encoder •••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

7SEG encoder ••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Conversion from gray code to binary code •••••••••••••••••••••••••••

BCD 6 digits up/down counter •••••••••••••••••••••••••••••••••••••••••••

24 bits shift register ••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Measurement of scan time •••••••••••••••••••••••••••••••••••••••••••••••

BCC code creation•••••••••••••••••••••••••••••••••••••••••••••••••••••••••

Display current value of the high-speed counter with sign •••••••••

2•59

2•60

2•62

2•63

2•65

2•66

2•67

2•69

2•71

2•72

2•73

2 - 1 Change of operation execution condition

●

Data processing application instructions consist of instructions which execute when input condition changes

●

from OFF to ON, and ones which execute every scan

cycle while input condition is ON.

a) Instructions to execute when input condition changes

from OFF to ON.

tween F-47 (set level operation condition) and F-48 (reset level operation condition).

●

F-00 (Data transfer between registers)

●

F-63 (Addition counter) etc.

To make item a) instructions execute each scan cycle

while input condition is ON, program its instructions be-

To make item b) instructions execute only when input

condition changes from OFF to ON, program F-44 (differentiate at ON state) after the input condition

Instructions F-47, F-48, and F-44 can be used more than

one time in a program so that different operation execution condition can be set for each instruction.

b) Instructions to execute for every scan cycle while in

put condition is ON (ON level operation).

F-12 (Comparison between registers)

F-141 (Jump to a label) etc.

1 scan

Scan cycle

04000

04000

F-63

INC

09000

09000

000

001

002

04000

F-63

INC

09001

ON level operation

F-47

ONLS

04000

09001

000

001

002

003

004

005

006

007

008

F-48

ONLR

1 scan 1 scan

04001

04001

04001

F-63

INC

04001

(Oscillating circuit)

09002

09002

000

001

002

003

004

005

F-47

ONLS

04000

F-44

↑

F-63

INC

09003

F-63

INC

09004

ON level operation

04000

04000

09003

000

09004

000

001

002

003

004

001

005

006

007

008

002

F-48

ONLR

2-1

2 - 2 Register clear

(1) Transfer of constant 0

(4) Subtract the same register

a.

F-01

BCD

00

09100

b.

F-07

DCML

000

09100

F-08

OCT

c.

000

F-11

SUB

09100 09100 09100

Fc15

MUL

09000

(5) Clear 4 bytes

09000

000

09100

Clear 4 bytes of 09000 to 09003.

(6) Clear n byte

(2) AND with constant 0

Fc13

AND

000

F-71

CONS

09100

000

09000 09077

Clear 64 bytes of 09000 to 09077.

(3) XOR with the same register

F-18

XOR

09100 09100

2 - 3 Masking data

04000

Fc13

AND

037

Necessary

data

Unnecessary

data

09200

0

1

1

09200

1

0

1

1

1

Be masked

AND

09200

0

0

0

1

0

1

0

1

1

1

1

1

0

Octal

constant

0

0

0

0

●

1

1

1

1

3

1

7

Any desired bit is set to 0 out of an 8 bits data.

Reference The JW30H and JW50H/70H/100H can mask

data using hexadecimal constants.

04000

0

Fx13

AND

1F

09200

0

0

1

2-2

F

1

1

2 - 4 Set/reset bits

(1) Set bits

04001

Fc14

OR

020

09110

Bits becomes 1

0

09110

0

0

0

1

0

0

1

Change in 1

OR

1

Octal costant

020

0

0

0

0

●

1

0

0

0

2

09110

0

0

0

1

1

0

0

1

0

0

Any desired bit is set to 1 out of an 8 bits data.

Reference The JW30H and JW50H/70H/100H can set bit

data using hexadecimal constants.

04001

Fx14

OR

10

1

09110

0

0

0

1

0

0

1

0

0

0

(2) Reset bit

04001

Fc13

AND

357

09110

Bits becomes 0

09110

0

0

0

1

1

0

0

1

Change in 0

AND

0

Octal constant

357

1

1

1

3

●

0

1

1

1

5

09110

0

0

0

0

1

0

0

1

1

7

Any desired bit is set to 0 out of an 8 bits data.

Reference The JW30H and JW50H/70H/100H can reset

bit data using hexadecimal constants.

04001

Fx13

AND

EF

0

09110

1

1

1

0

1

1

E

Reference For the JW20H, JW30H and JW50H/70H/100H,

1

1

F

bit set and bit reset instructions (F-133) are

available.

04000

Set/reset direction

04001

Set/reset

F-133

S/R

4

09110

4

7

6

5

4

3

2

1

When 04000 is ON

0

(Set)

0

09110 0

0

0

0

1

0

0

1

(Reset)

When 04000 is OFF 0

0

0

1

0

0

0

1

0

0

1

1

0

0

1

4

Bits becomes set/reset (0 to 7)

2-3

2 - 5 Decomposition of number

04011

F-00

コ0000 09000

XFER

コ0000 to 09000

Fc13

AND

Upper 4 bits are masked.

017

09000

F-55

コ0000 09100

SWAP

Fc13

AND

●

017

09100

Upper 4 bits of コ0000 are swapped with lower 4 bits and the result

are transferred to 09100.

Upper 4 bits are masked.

2 digits BCD number received from the input module is

decomposed into 1 digit number and stored in separate

register. In this example, lower 4 bits of コ0000 are transferred to 09000 and upper 4 bits to 09100.

コ0000 0

1

Octal constant

017

0

0

0

1

0

0

0

1

1

Octal constant

017

0

0

1

1

0

1

F-00

1 XFER 09000 0

1

0

Fc13

1 AND 09000 0

0

0

0

1

1

1

0

0

1

0

0

1

0

0

1

F-55

09100 0

SWAP

0

1

1

1

0

1

3

1

3

0

1

(Lower 4 bits of コ0000)

1

7

0

5

0

2-4

0

3

0

If 2 digits are used for input module in inputting multiple

number of 1 digit BCD numbers, it saves output module.

1

5

コ0000 0

●

0

1

0

1

(Upper 4 bits of コ0000)

1

7

Fc13

1 AND 09100 0

0

0

0

0

0

1

0

5

1

2 - 6 Composition of number

04002

F-00

09000 コ0040

XFER

09000 to コ0040

Fc14

OR

Upper 4 bits are set to 1.

360

コ0040

F-55

09100 09200

SWAP

Fc14

OR

F-13

AND

●

●

017

09200

09200 コ0040

Upper 4 bits of 09100 are swapped with lower 4 bits and the result

are transferred to 09200.

Lower 4 bits of 09200 are set to 1.

09200 is composed with コ0040.

09000 0

1 digit BCD numbers in two registers are outputted to

0

0

0

1

1

F-00

1 XFER コ0040 0

0

0

0

0

1

1

1

7

one output module. In this example , lower 4 bits of 09000

and 09100 are outputted to コ0040.

Octal constant

360 1

If 2 digits are used for output module in outputting multiple number of 1 digit BCD numbers, it saves output

09100 0

module.

0

1

1

1

6

0

0

0

0

0

1

0

3

0

0

0

Fc14

コ0040 1

OR

1

1

1

0

1

1

1

0

1

F-55

09200 1

SWAP

0

0

1

0

0

0

0

Fc14

09200 1

OR

0

0

1

1

1

1

1

9

Octal constant

0

0

0

0

1

1

1

1

7

1

1

1

1

0

1

1

1

0

コ0040 1

09200 1

0

0

1

1

1

1

09000

09100

F-13

コ0040 1

AND

0

0

1

0

1

9

1

1

1

7

Reference For the JW20H, JW30H and JW50H/70H/100H,

digit transfer instructions (F-69) are available.

04002

コ0040

09100

F-00

09100 コ0040

XFER

09100 to コ0040

0

F-67

NSFH

Shift lower 4 bits

to upper 4 bits

0

001

コ0040

9

0

9

9

コ0040

コ0040

Transfer lower 4 bits

of 09000 to コ0040

0

Upper shift

Input 0

コ0040

09000

F-69

09000 コ0040

NXFR

9

0

7

9

7

Digit transfer

2-5

2 - 7 Comparison with setting value

Setting value (octal)

00103

Fc12

コ0001

CMP

062

04000

07354

コ0001≧setting value

(Non-carry)

07354 07357

04001

コ0001>setting value

04002

07357

コ0001=setting value

(Zero)

07356

04003

コ0001<setting value

(Carry)

07356

Either one should be programmed

depending on application.

04004

コ0001≦setting value

(Carry)

07357

(Zero)

07354 07357

04005

コ0001≠setting value

(Non-carry) (Zero)

07356

(Carry)

The setting value must be programmed in an octal number.

(Ex. 1) In case that data in the register is a BCD number

BCD

〔Setting value: 50(BCD)〕

●

0

1

0

1

0

0

0

0

Octal

0

5

0

(Ex. 2)In case that data in the register is a binary number

BIN

〔Setting value: 50(BIN)〕

0

0

1

1

32

16

0

0

1

1

0

1

1

0

0

2

0

0

0

Octal

0

0

2

32+16+2=50

Reference To program the setting value in BCD and BIN

0

1

1

0

0

0

6

0

1

2

Transfer of the following to the register 09000.

F-01

BCD

50

09000

0

1

0

1

0

0

5

F-12

CMP

0

0

1

0

0

コ0001 09000

Transfer of the following to the register 09000.

F-07

DCML

F-12

CMP

2-6

050

09000

コ0001 09000

0

0

1

1

32

16

0

0

2

32+16+2=50

Reference For the JW30H and JW50H/70H/100H, comparison with hexadecimal set values using Fx12

instruction is also available.

00103

Hexadecimal

Fx12

CMP

コ0001

32

Reference With the JW30H, comparison instruction with

relay output (Fc180 to Fc185) is available.

00103

0

0

1

1

0

0

3

1

0

2

Fc183

コ0001

CP>=

062

04000

コ0001≧062(8) 04000 ON

Fc180

コ0001

CP>

062

04001

コ0001>062(8) 04001 ON

Fc182

コ0001

CP=

062

04002

コ0001=062(8) 04002 ON

Fc181

コ0001

CP<

062

04003

コ0001<062(8) 04003 ON

Fc184

コ0001

CP<=

062

04004

コ0001≦062(8) 04004 ON

Fc185

コ0001

CP<>

062

04005

コ0001≠062(8) 04005 ON

2-7

2 - 8 Window comparator

00100

Fc12

コ0000

CMP

07354

07357

(Non-carry)

(Zero)

Upper limit setting value

140

Data

Upper limit setting value

04000

コ0000>Upper limit

00100

07354

Lower limit setting value

Fc12

コ0000

CMP

07356

Lower limit setting value

120

04000

04000 04001

Upper limit≧コ0000≧Lower limit

(Non-carry)

(Carry)

04001

04001

04002

04002

07356

コ0000<Lower limit

(Carry)

●

When data is within the lower limit setting value and the

upper limit setting value, it makes 04001 turned ON. This

can be used for grading the acceptable from the unacceptable item (GO/NO GO).

●

In the above example, the upper limit setting value is to

140(8) (60 in BCD) and the lower limit setting value to

120(8) (50 in BCD).

It makes 04001 turned ON when 60≧コ0000≧50.

Reference Using Fc212 (window comparator), you can

execute this operation with one instruction.

JW30H and JW50H/70H/100H have window

comparator instruction (Fx212) with which

hexadecimal donation is applied for setting

values.

(1) Octal constant

(2) Hexadecimal constant

Lower limit Upper limit

Lower limit Upper limit

00100

07354

Fc212

コ0000

WNDW

00100

120

140

04000

(Non-carry)

07357

(Carry)

2-8

50

60

04000

(Non-carry)

04001

(Zero)

07356

07354

Fx212

コ0000

WNDW

07357

04001

(Zero)

04002

07356

(Carry)

04002

2 - 9 Comparator having undetectable zone

00100

Fc12

コ0000

CMP

Setting value LOW

120

Data

Setting value HIGH

04000

07356

(Carry)

00100

Setting value LOW

Fc12

コ0000

CMP

Setting value HIGH

124

04001

07354

04000

04001

(Non-carry)

04001

●

04000

When the output from the A/D converter is taken into the

●

In the above example, the high side setting value is set

input module, and compared a slight fluctuation in the

analog signal makes the A/D converter output affected

to 124(8) (50 in BCD).04001 turns ON when the contents

of コ0000 (to be a BCD code) is equal to or larger than

so that the comparison result by the sequencer may turn

ON and OFF. Use of this program permits the compari-

54, but it retains the ON state until the contents of コ0000

becomes smaller than 50, once after it has turned ON.

son without influence by the fluctuation in the A/D converter lower bits.

Setting value H

Setting value L

Comparison without

undetectable zone

Comparison with

undetectable zone

Reference Using Fc212 (window comparator), you can

execute this operation with one instruction.

JW30H and JW50H/70H/100H have window comparator

instruction (Fx212) with which hexadecimal donation is

applied for setting values.

(1) Octal constant

(2) Hexadecimal constant

LOW

00100

Fc212

コ0000

WNDW

HIGH

00100

120

124

04000

07356

(Carry)

07354

Fx212

コ0000

WNDW

LOW

HIGH

50

54

04000

07356

(Carry)

04000

04001

07354

(Non-carry)

(Non-carry)

07357

07357

(Zero)

(Zero)

04001

04001

04000

04001

2-9

2 - 10 Timer that multiple number of set points

00100

07360

(0.1s)

07354

TMR

100

1500

Setting value

To

Fc14

OR

040

コ0001

F-12w

CMP

コ0000

b0200

07360

Fc14

OR

コ0003

040

F-12w

コ0002 b0200

CMP

07354

04001

00100

(Non-carry)

04001

04000

00100

(Non-carry)

04000

コ0001,コ0000−Setting value T1, b0201,b0200 … Register that stores the TMR 100 current value

コ0003,コ0002−Setting value T2

●

By comparing the TMR current value with the setting

Note 1 The TMR current value is stored in the following

value in the register (or input module), it realizes the

timer that has a multiple number of set points.

format in bXXXX and bXXXX + 1.

7

6

bXXXX

00100

"8"

7

T0

TMR100

T0−T1

"4"

6

"2"

5

bXXXX+1

T1

T2

4

3

2

1

0

(×10−1)

"1"

4

"8"

3

"4"

2

(×102)

*

OFF OFF

04000

T0−T2

5

(×100)

"2"

1

"1"

0

(101)

1

8

4

2

1

With 1 in the bit of bXXXX + 1 marked with an aster-

04001

isk(*), it makes the timer operated.

The octal constant 040 of the figure below is ORed

by Fc14 and 1 is inserted in the position of an asterisk(*).

0

0

1

0

0

0

0

0

However, in the case of the JW10, bit marked with

* is always OFF. Therefore, Fc14 instruction is not

needed.

●

Also refer to “2-16 External output of timer current value”

and “2-18 Input timer setting value from an outside equipment.”

2-10

2 - 11 Obtaining the BCD result by the signed absolute value

S1

04000

F-11

SUB

F-11

SUB

S2

①

09000 09010 09020

}

Double length

operation

②

09001 09011 09021

07000

07354

07356

D

③

(Carry)

07000

103

102

09001

101

100

09000

S2

103

102

09011

101

100

09010

D

103

102

09021

101

100

09020

(Non-carry)

07356

F-01w

0000

BCD

(Carry)

F-11

SUB

F-11

SUB

●

S1

09100

④

09100 09020 09020

⑤

}

Double length

operation

⑥

09101 09021 09021

When subtraction of〈S1〉

〈S2〉is done using F-11, the

●

result will be obtained in complement.

(Ex.)1234−2612→8622 (complement of 10000)

It should be programmed in the above manner to obtain

the result in the signed absolute value. In this case, the

result is |S1−S2|=D and the negative sign (−) is outputted to 07000.

Carry flag

1,2

1

2

3

4

−

2

6

1

2

8

6

2

2

Complement of 10000

3

The carry flag is retained for the negative sign (-).

4

BCD constant 0000 is transferred to the register 09100,09101.

5,6

0

0

0

0

−

8

6

2

2

1

1

3

7

8

Absolute value

2-11

2 - 12 Multiplication of BCD 8 digits

S1

00200

S2

D

∼

*

F-15

MUL

09010 09000 09020

F-10

ADD

09022 09024 09022

F-15

MUL

09012 09000 09024

F-10

ADD

09023 09025 09023

F-15

MUL

09010 09002 09030

F-10

ADD

09026 09034 09024

F-15

MUL

09012 09002 09034

F-10

ADD

09027 09035 09025

F-10

ADD

09024 09030 09024

Fc10

ADD

09036

00

09026

F-10

ADD

09025 09031 09025

Fc10

ADD

09037

00

09027

F-10

ADD

09026 09032 09026

F-10

ADD

09027 09033 09027

Fc10

ADD

09036

00

09036

}

In case of ④×①+③×②,

Do carry processing.

∼

*

Fc10

ADD

09037

00

09037

S1 107 106 105 104 103 102 101 100

09013 09012 09011 09010

×)S2 107 106 105 104 103 102 101 100

09003 09002 09001 09000

S1×S2 1015 1014 1013 1012 1011 1010 109 108 107 106 105 104 103 102 101 100

09027 09026 09025 09024 09023 09022 09021 09020

2-12

09013

09012

09011

09002

09001

④

×)

09003

③

②

③×①

+)

④×②

09037

09023

09022

09027

09026

09025

09024

③×②

09033

09032

09031

09030

09035

09034

09020

09021

09020

09025

09025+09031

09026

09026+09032

09027

09027+09033

09022

09022+09024

09023+09025

09026+09034

09027+09035

09037+00

09021

09024

09024+09030

09036+00

09000

①

④×①

09036

09010

09023

09024

09025

09026

09027

09027

09026

09025

09024

09023

09022

Note 1 09030 to 09037 of register is used to temporality

store the intermediate result.

Reference With the JW20H, JW30H, and JW50H/70H/

100H, multiplication of BCD 8 digits data with

one F-15d instruction is possible.

00200

F-15d

09010 09000 09020

MUL

2-13

2 - 13 BCD 8 digits ÷ BCD 2 digits

●

F-16 is division instruction taking numerator as BCD 4

digits and denominator as BCD 2 digits. Division operation of BCD 8 digits numerator and BCD 2 digits denominator can be programmed with the following proceNumerator

Denominator

dure.

7

6

5

4

3

2

1

0

10 10 10 10 10 10 10 10

09003 09002 09001 09000

÷

1

Remainder

0

1

10 10

09010

Quotient

0

7

10 10

09024

6

5

4

3

2

1

0

10 10 10 10 10 10 10 10

09023 09022 09021 09020

Remainder

00200

7

F-16

DIV

6

5

4

F-00