EECS470 Homework 3 Answers

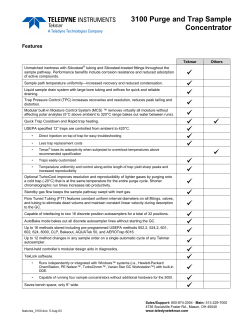

EECS470 Homework 3 Answers 1) False (WAR and WAW) dependencies. 2) Here is one example: DIVD F0, F2 F4 (10 cycles) ADDD F6, F8 F4 (2 cycles) The WAW dependency on F4 stalls the ADDD in dispatch on a Scoreboard machine. In a Tomasulo machine, the ADDD’s destination register is renamed and it can finish before the DIVD. 3) Having a larger set of architected can help if you have a large number of “live values”. That is values we have and will need in later computations. If you have enough architected registers, those values can be left in the architected registers. Otherwise you need to “spill” those values to memory (the stack) and “fill” them later when needed. Put another way, architected registers are a way for the programmer/complier to name things and keep them around without using loads and stores. Physical registers are not visible to the programmer/complier and cannot be so used. 4) A machine that implements precise exceptions ensures that trap instructions (and typically also external interrupts) are handled such that all effects of instructions prior to the trap are complete upon entering the trap handler, but none of the effects of instructions after the trap have occurred. In other words, the trap (or interrupt) appears to occur precisely between two instructions in the instruction sequence. Precise exceptions allow the system to resume execution where it left off after the trap is handled. 5) Software could periodically collect checkpoints of register and memory state. Any time an exception occurs, the software can handle the exception, and then restart execution from the most recent checkpoint. 6) Commit stalls if the instruction is not at the head of the ROB. 7) 8) See next page

© Copyright 2026