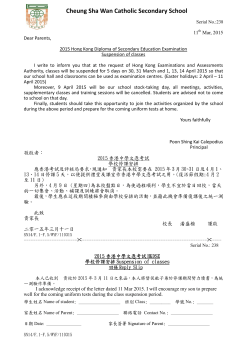

PDF version click here