A 1-V 1.8-MHz CMOS Switched-Opamp SC Filter with Rail-to

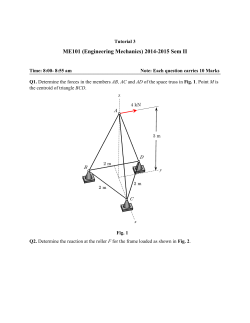

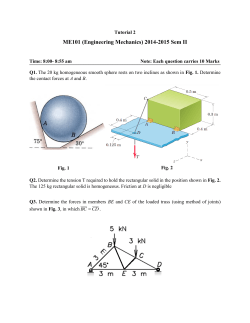

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 32, NO. 12, DECEMBER 1997 1979 A 1-V 1.8-MHz CMOS Switched-Opamp SC Filter with Rail-to-Rail Output Swing Andrea Baschirotto, Member, IEEE, and Rinaldo Castello, Senior Member, IEEE Abstract—A low-voltage switched capacitor (SC) filter operated from a single 1 V supply and realized in a standard 0.5-m CMOS technology is presented. Proper operation is obtained using the switched-opamp technique without any clock voltage multiplier or low-threshold devices. This makes the circuit compatible with future deep submicrometer technology. As opposed to previous switched-opamp implementations, the filter uses a fully differential topology. This allows operation with a rail-rail output swing and reduction of the number of opamps required to build high-order infinite impulse response (IIR) filters. On the other hand, a low-voltage common-mode feedback (CMFB) circuit is required. In addition, the circuit uses an opamp which is only partially turned off during the off phase. This enables an increase in the maximum sampling frequency. The filter implements a bandpass response (fs =fo = 4; Q = 7) and it has been characterized with a 1.8 MHz sampling frequency. Its power consumption is about 160 W. The filter is still fully functional down to 0.9 V supply voltage. Index Terms—Switched-capacitor filters. I. INTRODUCTION I N the last years, the interest toward low-power, low-voltage IC’s has consistently grown. This is primarily due to two factors: the increasing importance of portable equipment in all market segments [1] and the reduction of the supply voltage of modern IC due to technology scaling. On the other hand, it is mandatory to use the latest technology to be able to integrate increasingly more complex systems on a single chip. In the direction of single chip systems, CMOS technology appears to be the most advantageous, especially in terms of cost when a very large silicon area is needed. As a consequence, CMOS circuits operating at lower and lower supply voltages will be required as technology scaling progresses. Switched capicitor (SC) techniques have been demonstrated to be an efficient way of implementing analog functions in CMOS technology. The elements required for the realization of SC circuits are capacitors, switches, and opamps. Supply voltage reduction does not strongly affect capacitor properties. On the other hand, turning on and off MOS switches and maintaining proper opamp operation is difficult at low supply voltages. In fact, reducing the supply voltage correspondingly reduces the overdrive voltage of the MOS switches, and the classical approach based on the use of transmission Manuscript received April 16, 1997; revised July 17, 1997. This work was supported in part by CNR within “Progetto coordinato sistemi microelettronici a basso consumo per apparecchiature portatili.” The project has been developed within the ESPRIT TIBIA Project. The authors are with the Dipartimento di Elettronica, Universit´a di Pavia, 1-27100 Pavia, Italy. Publisher Item Identifier S 0018-9200(97)08798-2. gate (complementary switches) is no more effective. Fig. 1(a) shows the standard noninverting SC integrator embedded in a closed-loop structure. Fig. 1(b) shows the conductance of a transmission gate in its on-state when it is connected to a for V. As is varied between zero and voltage , the conductance remains always larger than a minimum value gds . Fig. 1(c) shows the switch conductance for V. A critical voltage region centered around for which both switches are not conducting is present [14]. However, with rail-to-rail output swing, the output of the opamp crosses this critical region. It follows that any switch connected to the output of the opamp [S1 in Fig. 1(a)] will not operate properly. On the other hand, the correct operation of all the other switches of Fig. 1(a) (S2, S3, and S4) can be guaranteed by properly choosing the value of bias voltages , , and . A possible solution to correctly turn on the critical switch S1 consists of biasing the opamp output either close to ground or to the positive supply. This, however, limits the output swing to either one of the two regions shown in Fig. 1(c). On the other hand, at low supply voltage it is mandatory to maximize the output swing in order to achieve a sufficient dynamic range. This is because reducing the supply voltage leaves the noise constant, while the signal swing is reduced more than linearly with the supply. As a consequence, ways to properly operate the switches while maintaining railto-rail output swing must be developed. Three solutions to this problem have been proposed: the use of lower threshold voltage devices [3], [4], the use of an on-chip clock voltage multiplier [5]–[9], and the switchedopamp technique [10]–[13]. The use of low-threshold devices is a high-cost solution since it requires a special technology. Voltage multipliers, which generate clock phases higher than the supply voltage to drive critical switches, cannot be used in scaled-down technologies. The most attractive development up to now appears to be the switched-opamp technique. A noninverting switched-opamp SC integrator driven by a similar stage is shown in Fig. 2 [10]. The critical switch S1 is eliminated and its function is realized by turning on and off the opamp through switch Sa. When the integrator is used in a closed-loop structure and for zero input signal, steady state is reached when no charge injection in virtual ground occurs. Thus, the relationship must hold. As a consequence, a compromise between the achievable signal swing and the amount of overdrive voltage of the noncritical switches must be reached. The original V and design [10] uses mV, with a threshold 0018–9200/97$10.00 1997 IEEE 1980 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 32, NO. 12, DECEMBER 1997 (a) Fig. 2. Original switched-opamp integrator [10]. The paper is organized as follows. In Section II, the switched-opamp technique is discussed, and the improved version is presented in detail. In Section III, the opamp is described, emphasizing the solutions adopted to improve the turn-on time and to implement a common-mode feedback (CMFB) circuit compatible with the minimum supply voltage. In Section IV, the experimental results relative to a prototype filter which implements the proposed solutions are given. Section V draws some conclusions. (b) (c) Fig. 1. (a) Standard SC integrator, (b) switch conductance with VDD = 5 V, and (c) switch conductance with VDD = 1 V. voltage of 0.9 V. This solution gives an output swing of 550 mV that is about half of a true rail-to-rail solution. In addition, minimum supply voltage required is given by . This is much larger than the minimum required by an optimized opamp. In this paper, a modified version of the switched-opamp technique is presented. Improvements are proposed both at the system level and at the circuit level. At the system level, the SC integrator of Fig. 2 is modified in order to independently set the common-mode input voltages and the quiescent output voltage of the opamp. In this way, true rail-to-rail operation is guaranteed, and the minimum supply voltage becomes a threshold voltage plus just two overdrive voltages. In addition, a fully differential solution is adopted. At the circuit level, the opamp is modified to reduce its turn-on time. This allows the use of a higher sampling frequency. II. THE IMPROVED SWITCHED-OPAMP TECHNIQUE The original switched-opamp technique shows the following limitations. 1) The minimum supply voltage required for proper operation of the filter is given by [10]. In addition, for this supply voltage, the available signal swing is zero. 2) The opamp is completely turned off during one phase of the clock. This causes a long turn-on time during the other phase which limits the maximum sampling frequency. 3) A single-ended structure is used, allowing only noninverting integrators. Thus, extra inverting stages are needed to build high-order infinite impulse response (IIR) filters. In this work, solutions for all the above limitations are proposed as outlined below. 1) The minimum supply required is set by the opamp and is equal to . Furthermore, in any condition, a rail-to-rail output swing is obtained [12]. 2) The opamp uses a two-stage topology where only the output stage is turned on and off and the charge stored in the Miller capacitance is maintained during the off phase. This allows the use of a higher sampling frequency. 3) A fully differential topology is used. This gives, at no extra cost, the sign change needed to build high-order IIR filters. Fig. 3 shows the single-ended version of the proposed switched-opamp SC integrator structure. A voltage level shift between the opamp input common-mode voltage and the output quiescent dc-voltage of the opamp is implemented by switching between and ground and injecting a fixed amount of charge in the virtual ground. BASCHIROTTO AND CASTELLO: 1-V 1.8-MHz CMOS SWITCHED-OPAMP SC FILTER 1981 (a) Fig. 3. Improved switched-opamp integrator. X (b) during operation. (b) Continuous time Fig. 5. (a) Excursions of node analysis of the integrator after turn on edge. Fig. 4. Output swing comparison for the two integrators: line I—output swing for the proposed switched-opamp integrator (Fig. 3) and line II—output swing for the original switched-opamp integrator (Fig. 2). In steady-state condition (i.e., no charge injection in virtual ground) the following relationship must hold: . Choosing , and to ground, results in equality to , setting ensuring rail-to-rail output swing. This allows the simultaneous optimization of switch operation and output swing. All switches are connected either to ground (and realized (and realized with PMOS). Thus, the with NMOS) or to minimum supply voltage required for the switch operation is , where is the larger of the two threshold voltages (N-type and P-type). Notice that this is the same as the minimum supply voltage required for the operation of digital CMOS circuits. The difference between the original and the new circuit in terms of available output swing can be quantitatively estimated with a numerical example using typical technology and design V, V, . parameters, i.e., for Fig. 4 plots the maximum swing achievable versus the two cases. For the new approach (line I), proper operation equal to 0.85 V compared to a value of about starts at 1 V for the original one (line II). Furthermore, while for the new approach at V the available swing is already 0.65 V (i.e., rail-to-rail), for the original approach V the swing is still zero. This is obtained at the at cost of a 50% increase in the output noise power due to the . additional SC branch of A potential problem using equal to ground is the possible charge loss during the turn on transients. In fact, the inverting opamp input node is always connected to a reverse biased pn junction associated with the drain/source of the NMOS switch S4, as shown in Fig. 5(a). This bulk diode could be forward biased by sufficiently large negative voltage spikes caused by the charge injection and the finite speed of the opamp. Simulations show that for a 500-mV spike of 5 ns duration and assuming a minimum size junction, a 0.5-mV voltage error on a 1-pF integration capacitor at 100 C results. At the turn-on instant (while the opamp is not active due to its finite bandwidth) two voltage steps are applied to the injecting capacitors and , as shown Fig. 5(b). Capacitor is driven with a negative step (it is switched from to ground) and tends to decrease the voltage at , while capacitor is driven with a positive step (it is switched from to ) and tends to increase the voltage at . The negative spike can then be reduced ensuring that the positive contribution from is injected before the negative contribution from . This can be done in two ways: with a proper sizing of the switches and with the use of delayed clock phases [15]. Assuming that the two capacitors are connected simultaneously, the excursion of the voltage can be described in the time domain by the equation (1) where and connected to and are the impedance of the switches , respectively. Therefore, choosing 1982 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 32, NO. 12, DECEMBER 1997 Fig. 6. Complete low-voltage switchable opamp. the size of the switches in such a way that can always be made to move in the positive direction. Notice that the use of large size for these switches is not critical for the charge injection because they are not connected to the virtual ground. This approach can be improved by the use of delayed clock phases, usually adopted to reduce signal dependent distortion [15]. In fact, in addition to the longer time constant associated with , this capacitor is also driven with delayed phase 1 Nd. A further problem with the structure of Fig. 3 is the disturbance coupled into the circuit due to . An error in the size results in an extra offset, while all the noise present on is injected into the signal path. This problem can be greatly alleviated using a fully differential structure. In this case, any disturbance (offset or noise) injected by results in a common-mode signal which is rejected by the fully differential operation. The amount of the cancellation is limited by the mismatch of the two differential paths. III. LOW VOLTAGE OPAMP DESIGN At low supply voltage, stacked configurations (like cascode) must be avoided. As a consequence, multistage structures are used to achieve a sufficiently high dc-gain. In this design, the input and the output common-mode voltages of the opamp can be independently set. This allows us to independently design and separately optimize the input and the output stage. The complete two-stage switched-opamp topology is given in Fig. 6. The key point for the output stage is to achieve a rail-to-rail swing. As a consequence, a very simple structure is used with no cascode in the signal path (M9, M10, and switch M11). It can operate with a minimum supply voltage of . The input stage is the most critical block when the supply voltage is reduced. For a common-mode input voltage equal to ground, a p-type differential input stage is used (M1, M2, M3, M4, and M5). The signal path is then folded (M6, M8) to ensure proper operation at low supply-voltage [2]. The minimum supply voltage for the input stage is given by (2) where the first condition must be satisfied to guarantee that the three stacked devices M1, M3, M5 operate in saturation region (i.e., ). If is larger than , as is usually the case, the second term dominates and the minimum supply . This is voltage required by the input stage is the same voltage required by the output stage. The key target in the opamp design is to minimize its turn on time, since this limits the sampling frequency. In this direction, only the second stage is turned off acting on M11, while the first stage is kept active even during the off phase. is connected to the source of M6 The Miller capacitor voltage through switch MS. Placing the source of M6 one higher than ground allows the proper operation of switch MS with the same required by the opamp. When the output stage is turned off, MS is opened disconnecting from M6. The charge stored on at the end of the active phase is conserved and no charging delay occurs at the beginning of the next active phase. The fully differential structure requires a CMFB circuit able to operate in the presence of a large opamp output swing. This circuit is shown in Fig. 7. It is a modified version of the dynamic CMFB used in many classic fully differential amplifiers [8]. The opamp used in the CMFB circuit is a single-ended structure with PMOS input stage and input common-mode voltage equal to ground. During and phase 1, the main opamp is off, and capacitors ( pF) are charged to , and capacitor CCM is completely discharged. In the same phase, capacitors pF) are disconnected and remain charged. In CFF (CFF this way, capacitors CFF implement a zero which improves stability of the common-mode control loop. During phase 2, the loop is closed and all capacitors inject charge into CCMFB pF). The CMFB circuit steady state occurs (CCMFB when during phase 2 no charge is injected in the integration capacitance. This charge is given by . Therefore, with (i.e., pF) the output opamp common mode is set . to Table I gives the size of the devices in the opamp and Table II summarizes the opamp performance. The opamp bandwidth is such that for a feedback factor , a sampling frequency larger than 10 MHz should be possible, within a standard SC structure. However, in a BASCHIROTTO AND CASTELLO: 1-V 1.8-MHz CMOS SWITCHED-OPAMP SC FILTER 1983 Fig. 7. Low-voltage sampled-data CMFB circuit. Fig. 8. Prototype bandpass filter architecture. TABLE I OPAMP DEVICE SIZES TABLE II OPAMP SIMULATED PERFORMANCE switched-opamp solution, the settling time is increased by the delay required to wake up the opamp (about 75 ns at 1 V supply). This delay limits the maximum sampling frequency to about 7 MHz. metal levels and two poly layers which are used to implement all the capacitors. The filter is a biquad cell implementing a bandpass response with nominal center frequency equal to one fourth of the sampling frequency and nominal . The filter structure is shown in Fig. 8. A unit capacitance of 0.3 pF has been used and the capacitor values are the following: pF, pF, pF, pF, pF, pF, pF, pF. In a bandpass filter it is possible to IV. FILTER PROTOTYPE AND EXPERIMENTAL RESULTS Using the proposed solutions, a prototype filter has been realized within a 0.5- m CMOS technology featuring three 1984 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 32, NO. 12, DECEMBER 1997 Fig. 10. Frequency response (VDD = 1 V). Fig. 9. Chip photograph. use a capacitive input coupling . For a switched-opamp structure this is an advantage with respect to low-pass filters which require an input dc-coupling. The chip photograph is shown in Fig. 9. The chip area is about 0.15 mm . In a bandpass filter with ( is the sampling frequency, is the bandpass center frequency), a very large slew rate is required since output step as large as half the signal amplitude are present. This is not the case for a classical lowpass filter where is generally much larger than four. Due to this requirement, the filter performance (maximum clock frequency, linearity, etc.) depends on the amplitude of the input signal. This effect is shown in the following. All measurements were done with V. The filter consumes about 160 W. Fig. 10 shows the filter frequency response at different clock frequencies from 1.8 MHz to peaking (2 dB) results. 4.2 MHz. Up to 3.4 MHz, a small Beyond this sampling frequency, the peaking becomes more pronounced due to incomplete opamp settling. The following measurements were done with MHz. The total output noise is about 800 V . The immunity with respect to noise on the supply has been measured in terms of power supply rejection ratio (PSRR) in the passband, and in terms of power supply rejection (PSR) up to . The PSRR in the band 300 kHz–600 kHz is shown in Fig. 11. A PSRR better than 46 dB is measured. In addition, for frequency up to , the PSR always stays lower than 45 dB. These measurements demonstrate the validity of the differential solution which guarantees immunity with respect to noise on the supply, even if it is directly injected in the signal path. Fig. 12(a) and (b) shows the single-ended and the differential output signals, respectively. It can be see that the signal is settling even for a signal amplitude as large as 1.6 V . In this case (since the output common mode is set slightly higher than ), the peak signal is within 100 mV from the supply voltage. From these waveforms, it is evident that the switched opamp mechanism is based on the fact that during one clock phase the output signal is not available and the output node is tied to the power supply (return-to-zero). This Fig. 11. PSSR measurement. fact must be taken into account in the overall signal processing system embedding the switched-opamp filter. If the signal is processed in a continuous-time manner, the return-to-zero results in a gain loss of 1/2 and in a linearity degradation, due to the large output steps resulting in slew rate and glitches. These phenomena degrade the linearity of the continuous-time waveform, but they have no effect on the sampled version of the output signal and then they can be avoided with a signal resampling, as occurs when the switched-opamp filter is used in front of an analog-to-digital converter (ADC). In the following, linearity measurements have been performed extensively for the continuous-time output waveform, and for a specific case they have been compared to those obtained using only the output samples. For the overall continuous-time waveform, a 3% intermodulation (IM) is measured for two input signals of 500 mV . On the other hand, the 1% IM corresponds to two 400 mV input signals as shown in Fig. 13. The dynamic range (defined as signal /noise ) for 3% IM is about 52 dB. The total harmonic distortion (THD) is measured with an input frequency at kHz. The third harmonic at is BASCHIROTTO AND CASTELLO: 1-V 1.8-MHz CMOS SWITCHED-OPAMP SC FILTER 1985 Fig. 13. 1% IM measurement. (a) Fig. 14. 1% THD measurement. TABLE III FILTER PERFORMANCE (b) Fig. 12. (a) Output single-ended waveform with 1.6 Vpp differential input signal. (b) Output differential waveform with 1.6 Vpp differential input signal. folded at which for the specific bandpass filter (with ) is in the passband. The 1% THD corresponds to a 725 mV input signal and the 3% THD to a 1.1 V input signal, as shown in Fig. 14. For the case of two 700 mV signals, the output signal has been sampled and a fast Fourier transform (FFT) analysis has been performed. A 1.8% IM has been measured, while for the continuous-time waveform the IM is 4%. Table III summarizes the filter performance. Finally, the filter is still fully functional with a supply voltage as low as 0.9 V. Fig. 15(a) shows the frequency response for sampling frequency between 500 kHz and 3 MHz with 500 kHz step. On the other hand, for MHz, a higher sampling frequency can be used. Fig. 15(b) shows the frequency response with sampling frequency between 1 MHz and 9 MHz with 1 MHz step. 0.5-m CMOS 1V 160 W 1.8 MHz 6.6 435 kHz 1.6 Vpp 800 Vrms 725 mVpp 1.1 Vpp 800 mVpp 1 Vpp 52 dB -46 dB 0.15 mm2 Technology Supply voltage Power consumption Sampling frequency Q fo Max. output swing Total output noise THD 1% THD 3% IM3 1% IM3 3% Dynamic range (IM3 3%) PSRR Filter chip area V. CONCLUSION The possibility of realizing SC circuits operated down to 1 V supply in a standard 0.5- m CMOS technology with sampling frequency in the MHz range is demonstrated. The 1986 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 32, NO. 12, DECEMBER 1997 ACKNOWLEDGMENT The authors wish to thank F. Montecchi (University of Pavia) and A. Nagari (ST Microelectronics) for helpful suggestions and discussions. REFERENCES (a) [1] A. Matsuzawa, “Low-voltage and low-power circuit design for mixed analog/digital systems in portable equipment,” IEEE J. Solid-State Circuits, vol. 29, pp. 470–480, Apr. 1994. [2] R. Castello, F. Montecchi, F. Rezzi, and A. Baschirotto, “Low-voltage analog filter,” IEEE Trans. Circuits Syst. II, pp. 827–840, Nov. 1995. [3] Y. Matsuya and J. Tamada, “1 V power supply low-power consumption A/D conversion technique with swing suppression noise shaping,” IEEE J. Solid-State Circuits, vol. 29, pp. 1524–1530, Dec. 1994. [4] T. Adachi, A. Ishikawa, A. Barlow, and K. Takasuda, “A 1.4 V switchedcapacitor filter,” in IEEE 1990 Custom Integrated Circuits Conf., pp. 8.2.1–8.2.4. [5] J. F. Dickson, “On-chip high-voltage generation in MNOS integrated circuits using an improved voltage multiplier technique,” IEEE J. SolidState Circuits, vol. SC-11, pp. 374–378, June 1976. [6] Y. Nakagone, H. Tanaka, K. Takeuchi, E. Kume, Y. Watanabe, T. Kaga, Y. Kawamoto, F. Murai, R. Izawa, D. Hisamoto, T. Kisu, T. Nishida, E. Takeda, and K. Itoh, “An experimental 1.5 V 64 Mb DRAM,” IEEE J. Solid-State Circuits, vol. 26, pp. 465–472, Apr. 1992. [7] F. Krummenacher, H. Pinier, and A. Guillaume, “Higher sampling frequency in SC circuits by on-chip clock voltage multiplier,” in 1983 European Solid State Circuits Conf., pp. 123–126. [8] R. Castello and L. Tomasini “A 1.5 V high-performance switchedcapacitor filters in BiCMOS technology,” IEEE J. Solid-State Circuits, vol. 26, pp. 930–936, July 1991. [9] J.-T. Wu, Y.-H. Chang, and K.-L. Chang, “1.2 V CMOS switchedcapacitor circuits,” in IEEE Int. Solid State Circuits Conf., Feb. 1996, pp. 388–389. [10] J. Crols and M. Steyaert, “Switched-opamp: An approach to realize full CMOS switched-capacitor circuits at very low power supply voltages,” IEEE J. Solid-State Circuits, vol. 29, pp. 936–942, Aug. 1994. [11] V. Peluso, M. Steyaert, and W. Sansen, “A switched-opamp 1.5 V–100 W modulator with 12 bits dynamic range,” Europ. Solid State Circuits Conf. (ESSCIRC 96)—Neuchˆatel, Sept. 1996, pp. 256–259. [12] A. Baschirotto, R. Castello, and F. Montecchi, “Design strategy for lowvoltage SC circuits,” IEE Electron. Lett., vol. 30, pp. 378–379, Mar. 3, 1994. [13] R. Castello, A. Baschirotto, and A. Nagari, “Low voltage, large swing, switched-capacitor circuit employing switched operational amplifier,” European patent (published) 94 830 318.5—Japan patent (pending) 7183434—U.S. patent (pending) 326 107. [14] E. A. Vittoz, “The design of high-performance analog circuis on digital CMOS chips,” IEEE J. Solid-State Circuits, vol.SC-20, pp. 657–665, June 1985. [15] D. G. Haigh and J. T. Taylor, “On switched-induced distortion in switched-capacitor circuits,” in IEEE Proc. ISCAS, May 1988, pp. 1987–1990. 16 (b) Fig. 15. (a) Frequency response with VDD : V. with VDD = 12 = 0:9 V. (b) Frequency response circuit is implemented with the switched-opamp technique, thus it does not require any clock voltage multiplier. Several new techniques have been proposed in order to solve critical limitations present in the previous switched-opamp circuits. In particular, the paper has presented a fully differential structure that improves dynamic range (rail-to-rail output swing is achieved) and an optimized opamp design that increases the possible sampling frequency. This design demonstrates that it is possible to achieve, with the SC filter operating at 1 V, performance comparable to that achieved with circuits operating at higher supply voltages. Andrea Baschirotto (S’89–M’95), for photograph and biography, see p. 932 of the July 1997 issue of this JOURNAL. Rinaldo Castello (S’78–M’87–SM’92), for photograph and biography, see p. 932 of the July 1997 issue of this JOURNAL.

© Copyright 2026