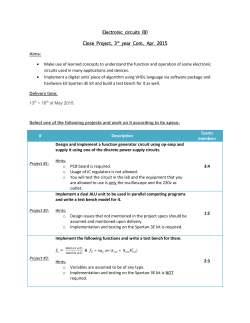

Microwave Circuit Design: A Practical Approach