Application Note AN897 "MC68008 minimum

AN897

MO~OROLA

@

Appliution

Semiconductor Products Inc.

Note

,,

MC68008 MINIMUM CONFIGURATION

SYSTL&&

\(c,.,,.

*:

~,1,.

.~.:,

i.~

.!..},,

:>

~~~.

,,

~+r+

>

*

,\/

\\~.,

:~

,,.

‘:-.:,>

~~””

,.*

.&.

.\:,:

-~)~.

.,,e,

....,.:~>”.~

Prepared by

.!:*’,*, ,.,~:,::~

‘s.::<$,.$

...

Geoffrey Brown and Kyle Harper

....~.~..y,.

....... X..,..

,:.,

-t..

..!,,:?,

Advanced Microcomputer Applications Engineering

~iij$,t,~

$?:$ ::&:,$j:$

,

Microprocessor Division

$$t,,:$>,

Motorola Inc.

..*\.*i$.

.:>,:1

~~..+~k

~.:,,

Austin, Texas

,+j:~$

~. ~~J\..*

*$.3

.$,.x

:?.~~::~,$

.,~,,,

,,.(,:.’

-’,:~,..

~~,$~’,,.:..

*,;<t

~

k ‘

,:$:{,’’~:~“‘

**

.,..

.$a\i

i><..

..,\?>

.*.<,,..

,,.,:i:<<.$\\

(~S) by~~~r$essor

and are terminated by the assertion of

INTRODUCTION

data twer’acknowledge

(DTACK) by the peripheral or

This application note demonstrates the design of a simple

m~~o~’’:device being addressed. Figures 1-4 show the

high-performance MC68~8 system that uses the MC68681

.~~n~um hardware necessary for an Mc68w8 system conDual Universal

Asynchronous

Receiver Transmitter

~~vs;~ng ok

(DUART) to interface with external devices. The MC68W8 is

*),J

~T*’*~ddress

decode logic,

an exce~ent low-cost alternative to the MC68W

and

.~\,~\

,>

,..t!’.)

features an 8-bit data bus while maintaining software com“S$~~~YrDTACK generation logic,

patibility with the rest of the M68~ Family. TheMC68681

.$ “

Reset logic,

DUART is an M68~

Family data communications X,@jp Bus error generation logic,

i*,\N

i’<.

that features:

..,,., *1

System memory,

TWO independent asynchronous sefial ch~nels

,$@~~&.

,,.+?.

*$):~\*

Interrupt handting logic, and

.<:$1,

~. ,k.

A programmable l~bit counter/timer,

,,$;.,

~~**

...,.<.+

+I$++<,i:$

An

MC68681 interface.

.. ‘{:>,..$,

.

A 6-bit pardel input port, and

“’’~...

‘+...-.

!,....*<i.,

,,,<

:2$%,

\,,\ ~’s

The following paragraphs detail the required hardware as apf$;i,..J.

:$.~

An 8-bit pardel output port.

pfied to the design concept described in this application note.

Emphasisin this design concept is pl~@~~~& performance,

expandabihty, and low chip COU~$<,~?~):,,,3

The M68~ system design p#@&~~ei’demonstrated in this

application note include: ,,,~t$:e>~kvs~

Interrupt hardware, ~ ‘?~~.*

.i~>;~’.

Peripheral interfac~@ ,,

Memory inter f~ce;~e&&ques,

Memory ref&@~,@itration in an M68~ system, and

Efficient,<~{#,&O software.

The s~te~~’~escnbed in this design concept, features the

foHo,#Wwme:

,ig&~~*

MC68W

microprocessor,

+$~%ytes of ROM,

&K bytes of dynamic RAM with no wait states, and

An MC68681 DUART.

The following paragraphs describe the hardware required

for a h~gh-perforrnance, expandable, low chip count

MC68M8 system fouowed by a description of the software

necessary to initialize and drive the MC68681 DUART.

HARDWA~

REQU=MENTS

The MC68~8 has an asynchronous bus structure in which

bus cycles are initiated by the assertion of address strobe

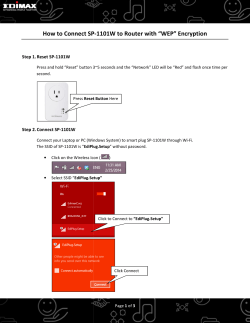

Address Decode Logic

The only tricky part of address decoding for an MC68W8

system is that the system ROM must be mapped to address

$m

at reset. It would be impractical to fti the ROM at the

bottom of the address map, as this would not tiow for

dynamic programming of interrupt vectors. To provide

dynamic mapping of these interrupt vectors, an SN74LS164

shift register (U28) is used to generate a signal, MAP, which

is low for the first eight memory cycles after reset (the

number of cycles necessry to fetch the reset vector and stack

pointer). U28 is reset rdong with the processor and is clocked

by the rising edge of ~. The ~

signrd generated by U28

is used by the address decoding circuitry to force selection of

ROM when MAP is low and to dow normal memory

decoding when ~

is high.

In the design given in this application note, address

decoding is accomplished by a PAL16L8 (U22). This PAL is

programmed to generate eight chip-select signals from ten input signals. The inputs to the PAL are the upper eight address tines (A12-A19), IACK (the NAND of the MC68W8

function code lines, FC&FC2), and the MAP signal. Four of

the PAL-generated chip-select fines are used in this design to

locate RAM at the address $m,

ROM at $A~,

and the

MC68681 at $F~.

The four remaining chip-select tines are

avaflable for future system expansion.

m

I

ROMDTACK

5

.

RAMDTACK

DUARTDTACK

‘s

+5V

U25

U21

A

GQw

A:

m

RIW

AS

m

A@A15

A6

Mll

I

4

,2

RFA5

RFA4

All

All

)

9+

3

13

1A

M

w

U2

ion

Ill

~6

A2

RFA3

,Ym;

RFA2

,,,

,

,

.,,.. .,,

,

,

II

11

1{

,”

RFA1

U17

RFAO

14

2

(I

<.

MUX +

SELECT~<

R FAO-RFA6

+-~

~-[,

~-~

‘~’t,:l,,.,,,,.

s.j,.. ..... .. ..

..

.,

,,

,-

~-,

gu,l,,

Vv

I

5

~

9

\8,

“36

fl

%

Ts

+5V

12

4.7 k

10

12 DPRQ

I

K

,+

U31B

*

Q b“

*

A2 7

Al

“u1 RS1

‘3

m

11

-&13

A~

To

RESET

R/~

lArKF4

,,

.-. .”

12

U27

-

3.6664 MHz

:J:,

s> $

~~

>i,t~<.,

,,,..,~!,~:t:>,i,.\>\v’

~+.,,,fA$,**’f

.tw,

~T:.J.,

),*,“,

, ... .

3

8

37

RESET

R/w

—

. .

32 i

HxUA

- --

, -,.=

‘$:

Ul, U2, Ull,

U3-U1O

U12

U13

U14

U15, U16

U18

U19

U20

U21, UM

U22

U23

U24

U25

U26, U27

U28

U29

U30, U31

U32, U36

U33, U35

U37

u%

U39

U17

SN74S 153

MCM666E j-15

McW~l

.-----LB

SN“

-. .74 LS146

SN74LS136

MCM68766

MC66661

CK17AI

cQaQ

SN74LS04

PAL16L8A

SN74LS05

SN74LS08

SN74S1O

SN74532

SN74LS164

MCN56

.SN74F74

DDu4-51m

SN74LS175

K1114A, 8 MHz OSC

MC1466

MC1489

DTACK Generation Logic

There are three possible sources of DTACK:

DUART DTACK,

asserted during both types of RAM cycles (normal and

refresh). CAS is generated only during normal cycles and

must be held asserted until the processor removes ~. In

order to accomphsh this, the appropriate delay tap (80

RAM DTACK, and

nanoseconds) is used to clock the SELECT signrd through a

ROM DTACK.

flip-flop (U31B). This fllp-flop is cleared when ~

is

The DUART generates its own ~K,

=

for RAM

negated. The output of this flip-flop is used for both the

is generated by the RAM control circuitry, and DTACK for

CAS signal and for the RAM DTACK. The 8 MHz MC68008

ROM is generated by an SN74LS175 quad flip-flop (U33).

allows the DTACK to be asserted up to 90 nanoseconds

These three DTACK sources are NANDed together by U25

before data from memory is vafid on a read cyc~,,The

and U21 to generate one processor DTACK.

specifications

for MCM6665L15

dynamic ,,*”~ *ies

guarantee that data is valid 75 nanoseconds af&g@$

.

9

Reset Logic

The memory refresh controller operates o~~~~~d~ciple of

There are two sources of system reset:

cycle stealing. Refresh requests may o~,!.er

between

Power-up reset, and

MPU bus cycles. If an MPU RAM c~@~~e&.&stoccurs durPushbutton reset.

ing a refresh cycle, it will not be starte~~~~l the refresh cycle

is finished. At periodic interv~~~

~‘Free-running clock

Power-up reset is generated by the timer (U29B) which pro(U29A) clocks a fip-flop (U3$,A) ~#generate a refresh reduces an active high pulse of approximately one-half second

quest. This refresh reque$+~~+l~chronized with the MPU

duration. The pushbutton reset, which allows the user to

~w~~t

clock by two fip-flOpS

reset the system without powering down, is generated by a

The MC68008 ac ,ati’i~l

specifications guarantee one

debounced switch. These two reset signals drive RESET and

falling

clock

edge

d~*]~e~S

high time and that there will

HALT through SN74LS05 open-collector drivers (U23).

beat least a on~%~df~ck period of ~S high time following

Bus Error Generation Logic

that clock ed@~$j*bitration between MPU and refresh reThe bus error signal, BERR, is generated by an

quests ocw%:~~ing this one-half clock period. The refresh

SN74LS175 quad fip-flop (U35). U35 counts clock pulses

reques~ijskc~nizer

consists of two SN74F74 flip-flops

that occur after IS becomes asserted. If ~ is stilI asserted

(U30)St~#e*~rst flip-flop (U30A) has as its input the refresh

after four rising edges of the E clock (between 5 and 6.5

r~hest ~%gndfrom the refresh request flip-flop (U3 1A) and

microseconds), U35 will generate BERR.

~i,r~[%%fked by the MPU clock. The second flip-flop (U30B)

~~h% as its input the output of the first synchronizer fip-flo~

System Memory

‘*,~k{.#30A) and is clocked by the MPU clock qualified by ~

The MC68008 system presented here has a system memory

‘~~$~~~~$

high. This two-level synchronizer is used to ensure that there

that consists of 16K bytes of ROM and 64K bytes of dynamic

RAM (see Figure 2). Because system performance is critical ,,$ ‘: will be no risk of the first synchronizer flip-flop (U30A)

entering a metastable state due to a missed setup time, The

in this design, a fairly complicated, but fast, dynamic *

‘

output of the synchronizer fllp-flop (U30B) is the SELECT

control circuit has been designed (see Figure 3). This.wlr~t

signal. Al three fllp-flops of the refresh circuitry are cleared

uses tw~elay

lines to sequence RAS and to a~wy,the

after the C=/RAMDTACK

flip-flop (U31 B) has been

MUX, CAS, and DTACK sigmds. Delay lines @S,,Y~@ssary

clocked during the refresh cycle. Address multiplexing for

in order to optimize memory cycle times and %~$~~$~ossible

the RAM is done by four SN74S153 multiplexer (Ul, U2,

to design the memory controller such th~$x~ystem

can

......$,.,

.. .2,,

.~i~,:l:

,

U11, and U17) with the appropriate addresses routed to the

operate without wait states.

\\,

RAMs by SELECT and MUX. Refresh addresses are

A description of RAM refresh req~~~$hronization

and

generated by an SN74LS393 dual 4-bit counter (U19) which

arbitration is given in the followin&)}~a@graphs. Note that,

is clocked by the refresh clock.

for now, a signal called SELE@~;~$3umed

which initiates

refresh cycles. The principl~,~#~i&rnents of this signal are

Interrupt Handting Logic

that it occurs periodically~d

‘&at it becomes asserted only

The interrupt handling logic must prioritize incoming

while ~ is negated. IR’add)~~n, the RAM decode signal is

interrupt requests and generate interrupt acknowledge

quafified with =S i~~&&#e$stocreate a RAM request signal.

signals back to the interrupt sources. Interrupt prioritization

Either the SELE.&~$$kl

or the RAM request signal may

is accomplished with an SN74LS148 8-to-3 priority encoder

initiate a RA~,&~G~&R

(U13). The MC68008 supports three of the M68000 interrupt

The front<~n@\~~%heRAM controller consists of three OR

levels (interrupt levels two, five, and seven); therefore, only

gates (U* @o&ed by a three input NAND gate (U25)

two of the outputsofU13 are connected to the MC68008. An

which in ~~~eeds into the first delay line (U32). Each of the

SN74LS138 3-to-8 demultiplexer (U14) is used to generate

thre~,~~ ~%+eshas as one of its inputs a signal from the secIACK signals for interrupting devices. The SN74LS138 is

o~~ %~y:]ine (u36) which changes state in the midde of the

enabled when ~S is asserted and FCO-FC2 are all high

rn~ti

cycle. The other inputs to these OR gates consist of

(indicating an interrupt acknowledge cycle). Because the

S~ECT,

RAM request, and an inverted feedback path

MC68681 uses ody one of the interrupt levels (interrupt level

from the output of the three input NAND. The initiation of a

five), the remaining two levels are available for future system

RAM cycle via either SELECT or RAM request causes the

expansion.

output of the NAND gate to go high. The output of the

The MC68681 Interface

NAND gate is then held high by the inverted feedback path

until the feedback from the second delay line forces it low.

With these logic circuits in place, interfacing the MC68681

The purpose of the feedback path from the second delay line

to the MC68008 is trivial (see Figure 4). The RESET, R/~,

is to guarantee that the delay lines will be cleared and ready

and data bus tines (DO-D7) are connected directly between

to begin another RAM cycle at the end of a cycle. The outthe MC68681 and the MC68008. The 1/0 chip-select line

puts of the first delay line generate the RAS, MUX, and CAS

generated by the address decode logic (1/0) is connected to

signals. Both the RAS and address multiplex signals are

the MC68681 chip-select (C=) pin. These address lines are

6

used instead of AO-A3 in order to maintain hardware design

consistency with the other M68000 Family microprocessors

(which do not have address fine AO). The MC68681 interrupt

(IRQ) and interrupt acknowledge (IACK) pins are tied to the

~ and IACK5 lines of the interrupt handhng logic, respectively, thus assigning the MC68681 interrupt a level 5 priority. Finally, a 3.68@ MHz crystal is connected between the

MC68681 X1/CLK and X2 pins. The crystal is required for

the on-chip baud-rate generator. 15 pF and 5 pF shunt

capacitors must dso be connected between the crystal and

ground as shown to ensure proper operation of the oscillator.

The MC68681 serial channels are connected to external

devices via RS-232 drivers and DB-25 connectors. The

MC68681

—

— OPO, _IPO, OP1, and IP1 pins are used as the

RTSA, CTSA, RTSB, and CTSB handshake fines, respectively; therefore, they too are routed via the RS-232 drivers

to their. respective connectors.

DINIT is the DUART initialization routine and is executed

upon system power-up. After DINIT initirdizes the DUART

channels, it enables channel A and channel B in normal

operation mode. INCH is the input character routine. Upon

entry, INCH requires the channel base address in address

register AO. Upon return, the lower byte of data register DO

will contain the received character. OUTCH is the output

character routine. Upon entry, OUTCH requires the channel

THE DUART SO~WA~

——

This design will use both of the channels and the RTS/CTS

handshake capabilities of the DUART. The interface software required for this design is flowcharted in Figure 5 and is

listed at the end of this document, There are three routines:

DINIT, INCH, and OUTCH.

OUTCHR

&&

FIGURE 5 – MC-

Minimum System Sotiare

Flowchans

MOTOROLA

M68000

ASM

vEQSION

1.30SYS

:

s.

.41NSYSS

.S~

07!20194

PAGElof4

73:k4:qa

MINSYSS

2

OPT

FRS)PCS,BRS

●

3

11

12

13

14

1s

16

17

la

19

20

21

22

;:

25

2b

27

28

29

30

000FOOO1

DUART

EQU

$OFOOO1

000FOOO1

000FOOOI

CHANA

MRIA

E au

DUARTtO

3UAET+0

000FOOO1

000 FOO03

000 FOO03

MR2A

SRA

CSRA

CRA

RaA

TBA

000 FOO05

000FOO07

000F0007

EQU

EQu

EQU

EQU

EQU

EQU

EQU

s

OUART+O

DUART+2

0UART+2

OUART+&

DUART+6

OUART+~.\{;

A

~

31

;:

34

3s

36

3?

38

39

40

000FOO09

000FOO09

000FOOOB

OOOFOOOB

000FOOO@

000FOOOO

000FOOOF

000FOOOF

IPC.R

ACR

INPUT

PORT

AUXILIARY

CHANGE

CONTROL

ISR

IMR

cMsa

INTERRUPT

INTERRuPT

ST4TUS

REGISTER

MASK

REGISTER

REGISTER

REGISTER

CTUR

CLS9

CURRENT

COUNTER/TIMER

COUNTER/TIMER

UPPER

CURRENT

COUNTER/TIMER

MOST

REGISTER

LEAST

CTLR

COUNTER/TIMER

LOWER

REGISTER

41

42

0UART+16

0UART+16

CHANNEL

B BASE

MOOE

REGISTER

AODRESS

19

43

44

4s

DUAQT+16

OUART+lB

MODE

29

DUARTt13

DUART+20

46

47

0UART+22

0UART+22

4a

49

:!

S2

S3

S4

;:

S7

OOOFOQf:h:\+~;<

OOOF@~*&”r$

ooQFQ&,b~

QQDFgoTb

$tibo,fholo

,:<.>t>~@~~#OOIF

,,?,

*,,,,*g:}:@~

’001 F

..,,.

“IVR

1P

OPCR

STRC

BTST

STPC

BTRST

*

*

CCNST4NTS

REGISTER

STATUS

REGISTER

a

CLOCK-SELECT

REGISTER

coMhANo

RECEIVER

REGISTER

BuFFER

TRANSMITTER

SIGNIFICANT

SIGNIFICANT

8

a

a

aUFFER

B

EQu

DUART+24

EQU

0UART+26

INTERRUPT

INPUT

PORT

EQU

EQU

0UART+26

DUART+2a

OUTPUT

PORT

START-COUNTER

CONFIGURATION

COMMAND

EQU

EQU

0UART+2a

DUARTt30

OUTPUT

PORT

REGISTER

aIT

SET

EQU

0UART+30

STOP-COUNTER

OUTPUT

PORT

COMMAND

REGISTER

BIT

RESET

VECTOR

REGISTER

(UNLATCHED)

REGISTER

COMMANO

COMMANO

BYTE

aYTE

w

98

91

93

.

.

This information haa bean carefully chackad and Is believed to ba entirely relisble. However, no responsibility is assumed for inaccuracies. Motorola reserves

the right to make changes to any products herein to improve rallability, function ordeslgn. Motorola does not assume any liability arising out of the application

or use of any product or circuit described herein. No license is conveyad under patent rights in any form. When this document contains information on a new

product, specifications herein are subject to change without notice.

MOTOROLA

@

Semiconductor

Products Inc.

Colvilles Road, Kelvin Estate - East Kilbride/Glasgow - SCOTMND

Printed in Switzerland

© Copyright 2026