negative resistance in gaas mesfet nonlinear modelling

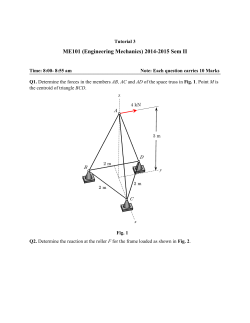

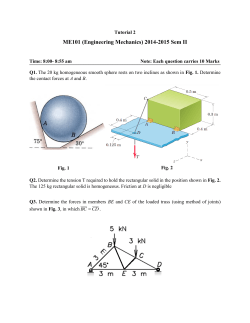

NEGATIVE RESISTANCE IN GAAS MESFET NONLINEAR MODELLING Friedrich Lenk, Ralf Doerner, and Peter Heymann Ferdinand-Braun-Institut für Höchstfrequenztechnik Berlin D 12489 Berlin, Rudower Chaussee 5 Abstract: In this paper the effect of negative resistance in the output part of a MESFET equivalent circuit is investigated. The essential feature is the introduction of an additional resistance. This modification improves model accuracy over the entire range of operating conditions. Finally, the results are used to develop an improved nonlinear model. INTRODUCTION Nonlinear transistor models for microwave application are based on multi-bias S parameter measurements. To extract the model parameters the device is driven into bias points not used under normal operating conditions, e.g. high voltage and high current. In particular, this is true for oscillator or power amplifier applications. There the device is driven into ranges where the validity of the standard small-signal equivalent circuit model is in question. This is most striking, when the measured |S22| exceeds unity /1, 2/. The tendency of |S22| to increase with frequency, however, can often be observed also in the normal operating regime. The effect can be explained by a stationary Gunn domain. It is nucleating at the drain side of the gate when the maximum electric field exceeds the threshold value for the negative differential mobility in GaAs /3/. We report experimental results on GaAs MESFETs, which prove the existence of a negative resistance in the drain part of the equivalent circuit. Accounting for the resulting variation in S22, the paper presents an extended small-signal equivalent circuit. In comparison to /4/, it agrees more accurately with the measured values. Furthermore, nonlinear modelling is improved by including the output conductance dispersion in the model. STABILITY CRITERIA To render Gunn oscillation possible, the parameters electron density n, device length l, and thickness of the active layer d of a structure must satisfy the following relations /5/: (1) nl > 1 × 1012 cm −2 and n d > 2 × 1011 cm −2 . These relations are fulfilled for the physical and geometrical active layer data of common GaAs FET structures . The typical values in a MESFET are n l ≈ 1.5×1014 cm-2 and n d ≈ 1×1013 cm-2. Also, the electric field exceeds the threshold value of Eth = 3.5 kV/cm. Nevertheless, stable operation is obvious and propagating domains have never been reported. This has been explained by two assumptions /6/: 1. The negative differential mobility does not exist in typical highly doped MESFET layers. 2. The transverse component of the electric field inside the active layer prevents the formation of a Gunn domain. Therefore, the current saturation occurs only due to saturation of the electron drift velocity. The general validity of this model becomes doubtful due to some recent publications /1, 7/ and the present investigation where negative resistances in MESFET equivalent circuits are definitely observed. The output current-voltage characteristics can be divided in three regions of operation /8/. The depletion layer thickness a under critical field condition in comparison to the active layer thickness d determines the operational mode: d<a pentode-like operation; no domain, a < d < 2a stable negative resistance; stationary domain, 2a < d Unstable region; propagating domain (high current). The thickness of the depletion layer depends on the gate voltage Vgs and is given by 2ε (Vbi − V gs + E th l g ) (2) a= q ND where q is the electron charge, ND is the doping density, Vbi is the built-in voltage, lg is the gate length, and ε is the dielectric constant of GaAs. We observed the negative resistance in a GaAs MESFET on MBE material with a doping density of ND = 5×1017 cm-3 and active layer thickness of d = 0.2 µm (under gate 0.25 1.2 measurement propagating domain 0.2 1 2a 0.15 stationary domain a<d<2a 0.1 0.8 common model 0.6 0.4 a 0.05 0 Mag S22 (lin) Layer Thickness d (µm) Depletion Layer Thickness a (µm) recess 0.1 µm). The gate length is lg = 0.5 µm. The corresponding conditions for domain formation are shown in Fig. 1. Over most of the range of gate voltages a stationary Gunn domain is expected (shaded area). This operating range exhibits a stable negative resistance (SNR) /8/, which is the focus of this article. no domain 0 0.5 1 1.5 Gate Voltage Vgs (V) 0.2 Fig. 1 Conditions for Gunn domain formation. Shaded area depicts the stable negative resistance (SNR) region /8/. Device Gated FET Ungated FET A 0.2 0.2 B 0.8 0.8 C 0.05 0.05 0 2 0 10 20 30 40 50 Frequency (GHz) 60 70 Fig. 2 Magnitude of output reflection coefficient of a 0.5×320 µm2 gate MESFET. Bias condition: Vds = 4 V, Id = 65 mA, Vgs = 0 V. Distance Source-drain Source-gate 6.5 2.8 10.0 Gate length 0.5 Width 320 34 Table 1 Physical dimensions of tested devices (units in µm). EXPERIMENTAL OBSERVATION OF THE NEGATIVE RESISTANCE IN GATED AND UNGATED FETS The effect that |S22| of a 0.5×320 µm2 gate MESFET exceeds unity at higher frequencies can be clearly seen in Fig. 2. To proof the existence of negative resistance an ungated FET structure on the same wafer was tested. Fig. 3 shows a schematic of the electrode and layer structure of the gated and ungated FET. The physical dimensions are listed in Table 1. Source Gate A B C Drain GaAs doped GaAs undoped AlGaAs undoped Resistance (ohms) 1000 500 0 -500 Semi-insulating substrate -1000 Fig. 3 MESFET layer structure. For data see Table 1. 0 1 2 3 4 5 Drain-Source Voltage Vds (V) 6 Fig. 4 Resistance of the ungated MESFET structure vs. voltage. Eq. (3) using data from Table 1 (solid line) and measurements (symbols). The differential resistance of the layer is given by dV 1 , (3) = dI d v( E ) qn wl dE where l and w denote length and width of the sample, respectively. We use the v(E) curve approximation from /3/ accounting for the constant mobility of µ = 3500 Vs/cm2 for E < 3 kV/cm and the negative slope for higher fields. The result for the ungated FET is shown in Fig. 4 compared with the resistance values extracted from the reflection coefficient in the frequency range 1–26 GHz. Measurements were performed with an HP 85109C VNA and a Cascade Microtech on-wafer equipment. LRM calibration has been used for all one- and two-port measurements. The good agreement shows that negative resistances really occur on this MBE layer structure and that the concept can be applied to the MESFET equivalent circuit. THE SMALL-SIGNAL EQUIVALENT CIRCUIT AND PARAMETER EXTRACTION The common direct extraction procedure of small-signal equivalent circuit parameter should lead to frequency-independent values /9/. With increasing frequency, however, often a decreasing real part of the output admittance Yds is obtained and may become negative in the SNR. Contrary to /4/, we suggest an extended equivalent circuit with a negative resistance Rdv in the output part. The common equivalent circuit and the extensions are shown in Fig. 5. G Lg Rg intrinsic Cgd Rgd Cgs Ri Rd Ld Vgsi Rdv b Cds Gds Cds Gds g m e -jωτ Vgsi D Cpg Cpd Rs a jωτ Cds |Gds| e ds Ls S Fig. 5 Common equivalent circuit and extensions to model the stable negative resistance regime. a. model extension acc. to /4/; b. model extension with negative resistance. After de-embedding, we get the admittance parameters of the intrinsic FET. The values of Ri, Cgs, Rgd, Cgd, gm, and τ are found to be frequency independent so that elements of the equivalent circuit are considered to model the FET correctly. The remaining variation of the output admittance Yds needs further treatment. Intentionally, the approach in /4/ should account for an increasing real part of Yds. It introduces a time-delay τds (insert a. in Fig. 5). This leads to a decrease of Re(Yds) with frequency and the transition to negative values shown in Fig. 6. Yds = Gds exp( − jω τ ds ) + jω Cds (4) This model restricts the maximum variation of Re(Yds) to the range from +|Gds| to -|Gds|. Consequently, the fit is not optimum for strong negative values at high frequencies. The novel approach introduces an additional resistance in the output part (insert b. in Fig. 5). Rdv represents the negative differential resistance of the Gunn domain. Now, the output admittance is described by Gds + jω Cds Yds = . (5) 1 + Gds Rdv + jω Cds Rdv Hence, the variation of Re(Yds) is enhanced to Gds Re(Yds ) ≈ at f → 0, 1 + Gds Rdv and Re(Yds ) ≈ 1 Rdv at f → ∞. Re(Yds ) (mS) Therefore, it is possible to fit two limits. The additional resistance Rdv can be obtained from the locus diagram of Yds, which is described by a circle with the center at 3/(2(Rds+Rdv)) and a radius of 1/(2Rds+Rdv). A linear regression to these circle parameters can be carried out. With radius and center known, Cds can be calculated at each frequency. To demonstrate that the effect does not appear only 1 at extreme ranges of voltage and current we present common model results at a moderate bias point of Vds = 3.5 V, 0.5 Id = 14.4 mA, Vgs = 0.25 V. This investigation was model acc. /4/ 0 performed for a 0.5×80 µm2 gate MESFET with fmax = 80 GHz on a MBE wafer. The extracted -0.5 equivalent circuit parameters are given in Table 2. A this work comparison of measured and calculated S para-1 meters is shown in Fig. 7. The improvement in S22 can be seen clearly from Fig. 8, where three -1.5 methods are compared. It shows that the effect of -2 negative resistance is not restricted to large gate 0 10 20 30 40 50 width power transistors. It can also be observed on Frequency (GHz) small sized FETs and can improve also the linear modelling. The equivalent circuit obtained by the Fig. 6 Comparison of measured real part of Yds common extraction method fits well all measured (symbols) and different model approaches. S parameters except S22. The reason is the improper modelling of the SNR. Taking into account the strong negative values of Re(Yds) at higher frequencies, the presented model is better suited to fit the measured values. It should be noticed that also the fit for S12 is improved when considering the Gunn domain. Cpg Cpd Lg Ls Ld Rg 10.2 fF 10.2 fF 39.9 fF 0 fF 24.4 fF 2.9 Ω 15.1 Ω 21.5 Ω 121.6 fF 3.3 Ω 4.8 fF 1.1 kΩ Rs Rd Cgs Ri Cgd Rgd gm τ Rds Cds Rdv 14.9 mS 3.34 ps 1.75 kΩ 11.7 fF -134.4 Ω Table 2 Equivalent circuit parameters of 0.5×80 µm2 gate MESFET. Bias condition: Vds = 3.5 V, Id = 14.4 mA, Vgs = 0.25 V. 90° 1.6 0.08 1.2 1.2 0.06 1.1 0.4 0.02 180° 0.0 0.2 0.5 1.0 2.0 5.0 0° Mag S22 (lin) 0.8 0.04 this work 1 model acc. /4/ 0.9 -5.0 -0.2 common model 0.8 -2.0 -0.5 0 10 20 30 Frequency (GHz) 40 50 -1.0 Fig. 7 Comparison of measured (symbols) and calculated (solid lines) S parameters 1– 50 GHz. Equivalent circuit parameters and bias condition acc. to Table 2. Fig. 8 Comparison of measured (symbols) and calculated (solid lines) S22 values. LARGE-SIGNAL MODELLING AND RESULTS In large-signal modelling, the small-signal transconductance gm and the output conductance Gds are calculated from the derivations of Id (Vgs, Vds) with respect to Vgs and Vds. Therefore, the transition from small-signal to large-signal model implies that gm and Gds are no longer modelled independently. In other words, they are connected as a parallel circuit. This makes it difficult to utilise the Rdv approach for largesignal modelling, since it violates this precondition. In contrast, the τds model could be described by a slight modification of the Id (Vgs, Vds) equation. In all common large-signal models an expression Id = Id (Vgs(t-τ), Vds(t)) is used. Under small-signal condition, this leads to ∂ Id = g m exp( − jω τ ) (6) ∂ Vgs Current I d (mA) and for the derivation of Id with respect to Vds to a frequency independent Gds. To take τds into account one has to use Id = Id (Vgs(t-τ), Vds(t-τds)) instead. Now, Id derived with respect to Vds reads: ∂ Id = gds exp( − jω τ ds ) (7) ∂ Vds Simulations are performed with HP EEsof / MDS. A 20 symbolic-defined device (SDD) with five ports is Vgs (V) = -1.25 (0.25) 0.5 used. The first port describes the input current as a 15 function of gate charge Qg. d I1 (t ) = Qg Vgs (t ), Vds (t ) , (8) dt 10 bias point where Vgs is the voltage applied to this port. In series the second port models a voltage-independent Ri. 5 Two auxiliary ports (closed by 50 Ω) are generating Vgst = Vgs (t-τ) and Vdst = Vds (t-τds). The last port describes the output current as 0 0 1 2 3 4 5 d I 5 (t ) = I d Vgst (t ), Vdst (t ) + Qd Vgs (t ), Vds (t ) (9) Drain-Source Voltage V ds (V) dt The current equation is according to Angelov /10/. Fig. 9 Output characteristics of a 0.5×80 µm2 gate A series circuit of linear R and C at this port is MESFET. Measured (symbols) and added. It takes the low-frequency dispersion of Gds calculated (solid lines) values. Bias point: into account. The measured and modelled output Vds = 4 V, Id = 11.2 mA, Vgs = 0 V. current-voltage characteristics of a 0.5×80 µm2 gate ( ( ( ) )) ( ( )) 90° 0.0 0.2 0.20 1.2 0.15 0.8 0.10 0.4 0.05 0.5 1.0 1.2 1.1 2.0 5.0 0° Mag S22 (lin) 80° 1.6 this work 1 0.9 -5.0 -0.2 common model 0.8 -2.0 -0.5 0 10 20 30 Frequency (GHz) 40 50 -1.0 Fig. 10 Comparison of measured (symbols) and calculated (solid lines) S parameters. Bias point as indicated in Fig. 9. Fig. 11 Comparison of measured (symbols) and calculated (solid lines) S22 values. MESFET is shown in Fig. 9. The indicated bias point was used to generate small-signal S parameters. They depend on the gate and drain charges Qg and Qd, respectively. These charges are modelled with modified Angelov expressions. The results in comparison to small-signal measurements are shown in Fig. 10. The detailed view of |S22| in Fig. 11 confirms the improved fit. The remaining difference to the small-signal model is due to the effect that the influence of τds is limited to the output current expression. CONCLUSION The MESFET equivalent circuit has been extended to describe the stable negative resistance operating regime. The time-delay approach eq. (4) and the negative resistance eq. (5) are compared. Both are suited to model the S parameters up to 50 GHz for normal bias points. The introduction of Rdv achieves better agreement for strong negative values of Re(Yds) as found at large drain-source voltages. The improved nonlinear model describing the output conductance dispersion reproduces small- and large-signal behaviour of the device under test better than the common model, also in the usual bias range. REFERENCES /1/ M. A. Magerko and K. Chang, "Modeling of Gunn Domain Effects in the Output Conductance of the High-Frequency Small-Signal GaAs MESFET Equivalent Circuit", Microwave and Optical Technology Letters, Vol. 5, pp. 748–752, 1992. /2/ K. E. Jones, E. W. Strid, and K. R. Gleason, "MM-Wave Wafer Probes Span 0 to 50 GHz", Microwave Journal, Vol. 31, pp. 177–183, 1987. /3/ M. Shur, GaAs Devices and Circuits, Plenum Press, New York 1987. /4/ U. L. Rohde, "Improving Noise Modeling of GaAs FETs. Part 1: Using an Enhanced Equivalent Circuit Technique", Microwave Journal, Vol. 34, pp. 87−101, 1991. /5/ H. Kroemer, "Negative Conductance in Semiconductors", IEEE-Spectrum, Vol. 5, pp. 47–56, 1968. /6/ P. H. Ladbrooke, MMIC Design, GaAs FETs and HEMTs, Artech House, Boston and London 1989. /7/ G. Leuzzi, A. Serino, F. Giannini, and S. Ciorciolini, "Novel Nonlinear Equivalent Circuit Extraction Scheme for Microwave Field-Effect Transistors", Proc. 25th EuMC, Bologna, pp. 548–552, 1995. /8/ K. Yamaguchi, S. Asai, and H. Kodera, "Two-Dimensional Numerical Analysis of Stability Criteria of GaAs FETs", IEEE Trans. Electron Devices, Vol. ED-23, pp. 1283–1290, 1976. /9/ G. Dambrine, A. Cappy, F. Heliodore, E. Playez, "A New Method for Determining the FET SmallSignal Equivalent Circuit", IEEE Trans. Microwave Theory Tech., Vol. MTT-36, pp. 1151−1159, 1988. /10/ I. Angelov, H. Zirath, and N. Rorsman, "A New Empirical Nonlinear Model for HEMT and MESFET Devices", IEEE Trans. Microwave Theory Tech., Vol. MTT-40, pp. 2258−2266, 1992.

© Copyright 2026