Pipeline Datapath

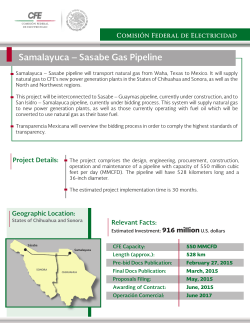

CS 2506 Computer Organization II MIPS 2: Pipeline without Forwarding You may work in pairs for this assignment. If you choose to work with a partner, make sure only one of you submits a solution, and that the file lists names and PIDs for both of you at the beginning. Prepare your answers to the following questions in a plain text file. Submit your file to the Curator system by the posted deadline for this assignment. No late submissions will be accepted. For all questions, show supporting work if you want partial credit. You will submit your answers to the Curator System (www.cs.vt.edu/curator) under the heading MIPS02. 1. [12 points] True/False questions. No justification is necessary. a) The speedup that can be achieved in a pipeline is unrelated to the number of stages in the pipeline. b) The primary reason to have the interstage buffers shown (in yellow) in the partially-completed pipeline design below is to synchronize the progress of instructions with the relevant control signals and data values. c) The clock cycle (the length of a clock period) in pipelining is determined by the average latency time required for all the stages. For questions 2 through 7, Refer to the incomplete preliminary pipeline design, shown below, which includes the interstage buffers needed to synchronize signals and data with the instructions, but no support for forwarding operands. This datapath supports execution of the following MIPS instructions: add, sub, and, or, slt, lw, sw and beq (assuming that data/control hazards are handled by inserting nop instructions and/or reordering instructions outside of the datapath). 3 2 4 5 You may work with a partner on this assignment! 1 CS 2506 Computer Organization II 2. MIPS 2: Pipeline without Forwarding [12 points] In the design given above, the MUX that selects the Write register number has been moved from the ID stage to the EX stage (versus the original single-cycle design). Also, the RegDst control signal that manages the selection is routed through the ID/EX interstage buffer before reaching the MUX. Suppose the designer had left the MUX in the ID stage, as it was before, and had simply routed the RegDst control signal directly to the MUX, as before. Also suppose the output from the MUX is then passed through the ID/EX, EX/MEM and MEM/WB interstage buffers, before being routed back to the Register file (as shown in the given design). Would this approach still deliver the correct Write register number to the Register file? Explain. 3. [12 points] Suppose the AND gate used to determine whether a conditional branch will be taken was moved from the MEM stage into the WB stage, and that its two inputs (Zero and Branch) were passed forward through the MEM/WB interstage buffer before being delivered to the AND gate, instead of being delivered to the AND gate in the MEM stage. Suppose the output from the AND gate was then routed directly back to the MUX in the IF stage (as is currently done). Would this cause any problems? Explain. 4. [12 points] Find (at least) two values that are stored in the EX/MEM interstage buffer that are not needed for the correct execution of an R-type instruction, and explain why the pipeline passes these values to the next stages. 5. [10 points] Suppose the change described in question 3 was made, and that nop instructions are inserted to guarantee that we do not fetch the wrong instruction after a beq instruction. Assume that a beq instruction enters the pipeline, and that the branch will be taken. Irrespective of whether the change would cause any problems, how many nop instructions will have been inserted into the pipeline by the time the branch target address is written into the PC? 6. Consider the following sequence of MIPS32 assembly instructions: lw add sub sw lw add $t3, $t0, $t1, $t3, $t0, $t4, 0($t0) $t3, $t3 $t0, $t3 4($t0) 0($t1) $t3, $t1 # # # # # # 1 2 3 4 5 6 A data dependency occurs when a later instruction requires an input value that is set by an earlier instruction. A data hazard occurs when one instruction writes a value into a register that will be used as input by a later instruction, but that value does not actually appear in the register by the cycle on which the later instruction attempts to read it. Note that a data hazard always implies a data dependency, but some data dependencies do not imply a data hazard. Also remember that this pipeline design does not include any provision for forwarding operands. a) [10 points] Identify the data dependencies that would NOT prevent the given sequence of instructions from executing correctly on the given hardware design above, even if we do not insert nop instructions. For each such dependency, list the register involved, the writing instruction and the reading instruction. b) [10 points] Identify the data hazards that would prevent the given sequence of instructions from executing correctly on the given hardware design above, unless we inserted one or more nop instructions. For each such dependency, list the register involved, the writing instruction and the reading instruction. c) [12 points] Rewrite the given sequence of instructions adding nop instructions so that the modified sequence would execute correctly on the given hardware design. For full credit, accomplish this with the smallest possible number of nop instructions. d) [10 points] How many clock cycles would be required to execute the modified sequence of instructions you gave in the previous part of this question? You may work with a partner on this assignment! 2

© Copyright 2026